此文章简单分享关于Intel VRTT 测试的相关内容,若有理解上的问题,欢迎指正

SVSC (Static Voltage Static Current),顾名思义,就是静态电压静态电流。

SVDC(Static Voltage Dynamic Current),静态电压动态电流

DVSC (Dynamic Voltage Static Current),动态电压静态电流

8 个赞

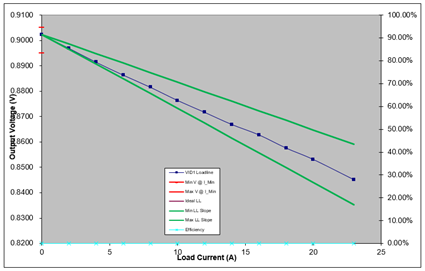

关于Load line

6 个赞

关于PS状态

CPU在不同的工作状态下对电流有不同的要求,多相电源在重载时肯定是满负荷全员上,但轻载时如果全员都在打开关工作,就有点浪费资源了,为了提升电源在轻载时的工作效率,引入了PS的概念。目前笔电测试有五种PS(Power Status)状态,它们的定义如下:

PS0:大功率工作,全相CCM意思就是所有的Dri-MOS都在稳定地打开关供应输出。

PS1:功率相对较小时选择这个状态,只有一个Dri-MOS在CCM工作,其余的MOS都进入待命。

PS2/3:功率更小,唯一工作的MOS进入DCM模式,更大地降低功耗,与普通DCDC相似,因为工作在DCM,输出纹波也会变大。

PS4:类似进入休眠状态,输出电压降为0V。

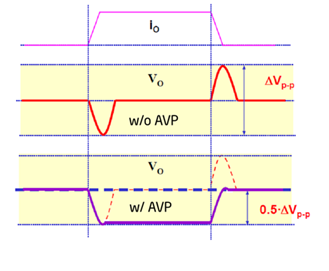

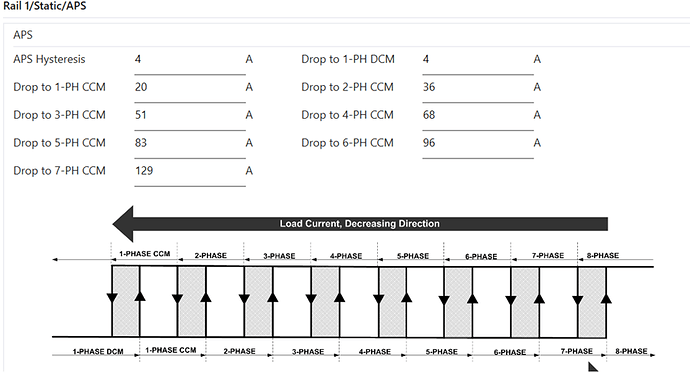

笔电测试中切换PS状态是靠CPU发切PS指令完成的,是被动的,但是服务器中切换Dri-MOS工作数量是我们的controller主动根据现有输出电流调节的,这种工作模式叫做APS(Auto-Phase Shedding),APS也是为了优化不同工作电流下的效率。

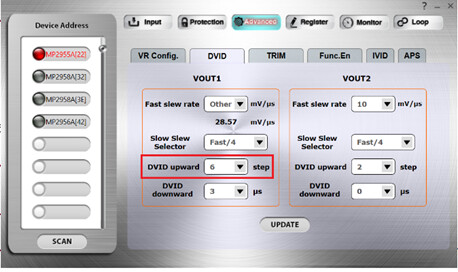

下图是MPS的GUI(可视化I2C调试小工具)内部APS的设置。从图中可以看出,随着输出电流从小往大走,我们的controller会自动控制一个个Dri-MOS参与工作,而随着电流从大往小走,controller又会控制一个个Dri-MOS停止打开关,在增加Dri-MOS和减小Dri-MOS的电流点有个滞回差值4A,这是为了防止在一个切phase电流点时,controller误判导致反复增加或减小Dri-MOS的数量

5 个赞

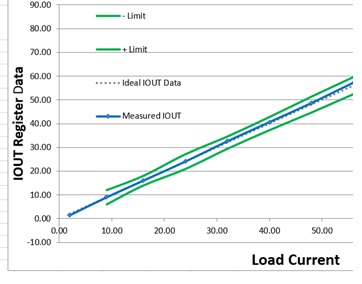

关于Imon(monitor监控电流)精度读取

CPU在抽取电流时需要知道电流是否已经足够支撑现在的运作,就需要通过SVID获取我们控制器这边sense反馈的电流值,看看是否抽载准确,从而来调整抽载的大小。

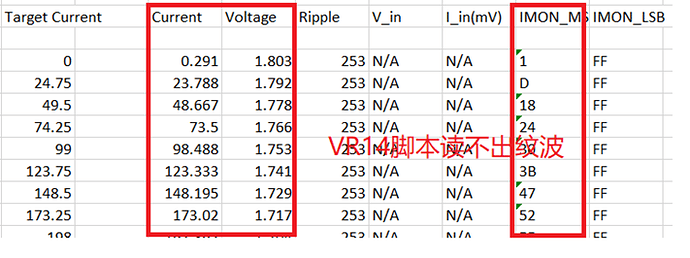

比如以下这个表格第一列代表测试工具抽的电流,表格第四列代表测试工具通过SVID读取的控制器自己sense的电流转化的16进制,表格会自动将十六进制转化为电流值,例子如下:

比如对应下表标红的一组数据,取自某次测试,Iccmax=128A,FF的十六进制可以将Iccmax 128A平分成256等分(256为十进制),当Imon回报的十六进制数据为20,转化成十进制就是32(可以用计算器转化),对应的电流就是256份里的32份,电流即可计算为I=128/256*32=16A

根据tool抽载和实际采样反馈的电流,测试表格会自动拟合一条曲线,看抽载是否准确,如果偏差不大,需要我们通过GUI(I2C)去微调controller里面的寄存器,如果偏差很大,就需要去debug电路中或者寄存器里是否有设置错误的地方。

Processor Test Current in (A)

Measured Static Voltage in (V)

Ripple in (mV) pk-pk

SVID Iout reading (HEX)

0

0.8995

12

0

2

0.8958

12

3

9

0.8833

14

12

16

0.8699

14

20

24

0.8544

14

30

5 个赞

关于DVID(动态电压,静态电流)波形测试中的时间测量

前面讲到这个测试需要我们输出电压以一定的斜率在限定的时间内完成调压以及在稳定时输出电压不低于规定的数值。电压切换的斜率有三种,fast,slow以及decay,其中每一个rail的fast和slow都有intel各自规定好的斜率,decay直译为衰减,可以看出它只针对输出电压从高往低调节,并且decay的时间不可控,所以遇到decay的测试,电压下降的时间我们一般不测量。

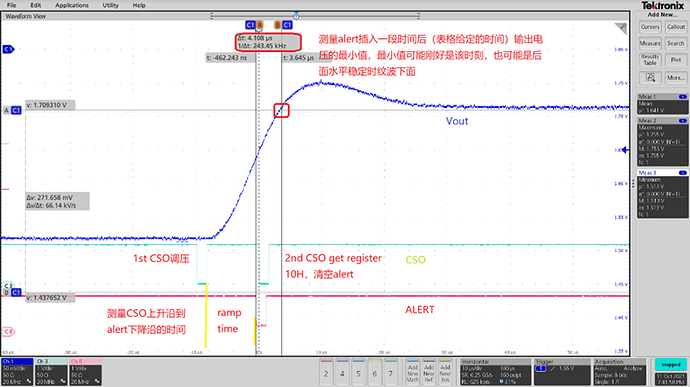

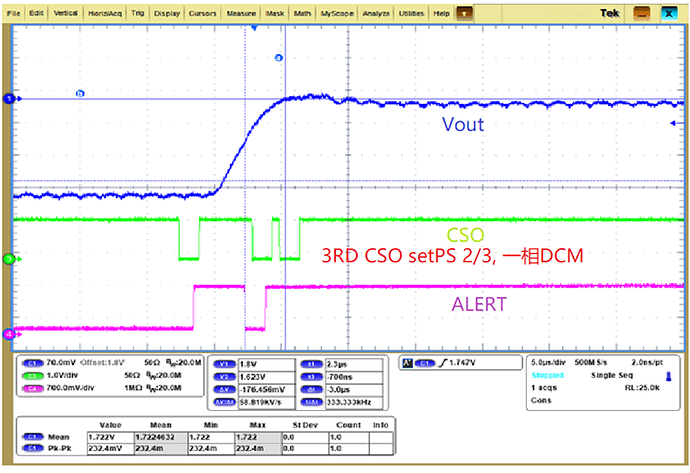

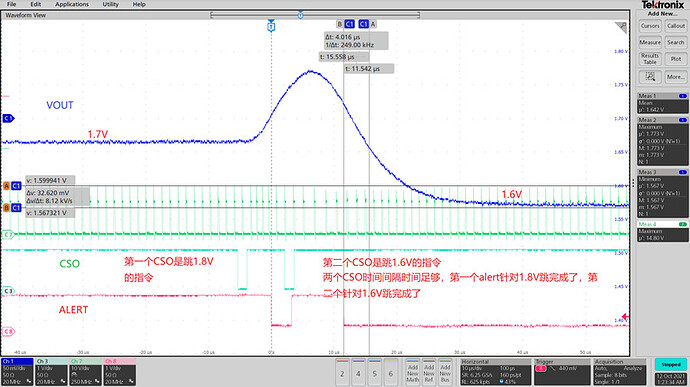

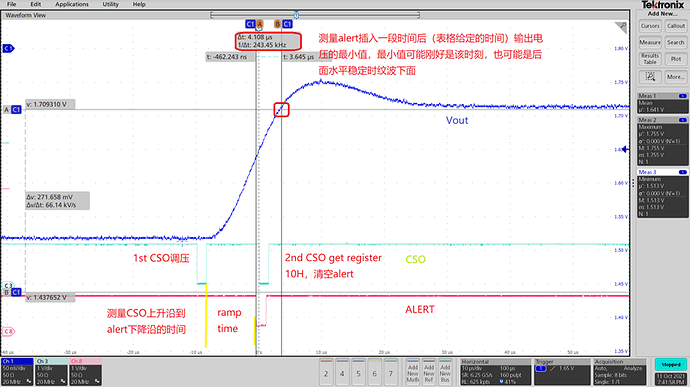

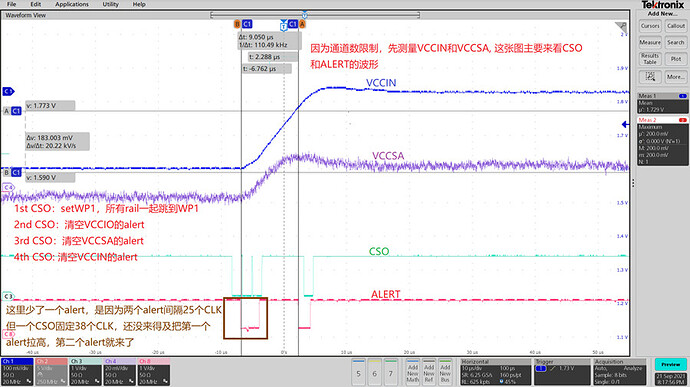

电压切换的时间怎么测量呢?下图为我们测试过程中截取的波形,图中有三个信号,一个是Vout,另外两个CSO和ALERT就是我们用来测试时间的信号。当CPU给controller发指令时,CSO会被拉低,当controller接收到指令并接受指令时,CSO又会回到高位,通常每个CSO会持续38个clk(一个clk为40ns),如果controller拒绝CPU发的指令,CSO就不会被拉高(比如还在DVID过程中,如果发了某些指令会被拒绝)。下图有两个CSO信号,第一个代表调压,第二个是发送get register 10H(用来清空alert,把alert重新拉高)。整个系统工作时,alert会在三种情况下被拉低,我们测试接触的是电压跳到指定的step了,alert会被拉低。测量调压时间卡的就是CSO上升沿到ALERT的下降沿,具体哪个CSO需要结合图片和测试表格给的条件,理解每一个CSO对应的含义。

前面测试时间时的alert是我们controller接收到调压指令后自己内部去数多少个step后拉低alert,而不是测量电压值拉低alert。我们controller通常会提前几个step拉低alert,比如测试中VCCIN从1.63V跳到1.83V,斜率为25mV/us,这时表格会限定时间不能超过200/25=8us,我们测试CSO上升沿到alert下降沿的时间就要小于8us才算pass。

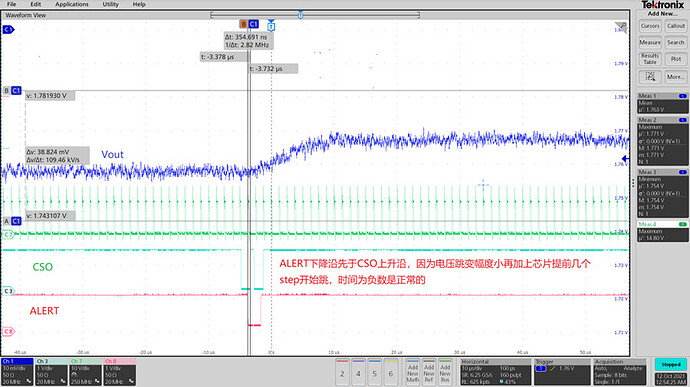

有时候ALERT会先于CSO上升沿导致测量的时间为负数,这是允许的,因为我们芯片会提早几个step去跳DVID,再加上有的测试电压跳变的幅度很小,比如1.81V跳1.83V,时间很短。如下图所示

下面来看一些测试中遇到的波形解析

A. 测试中常见的CSO和Alert波形解读

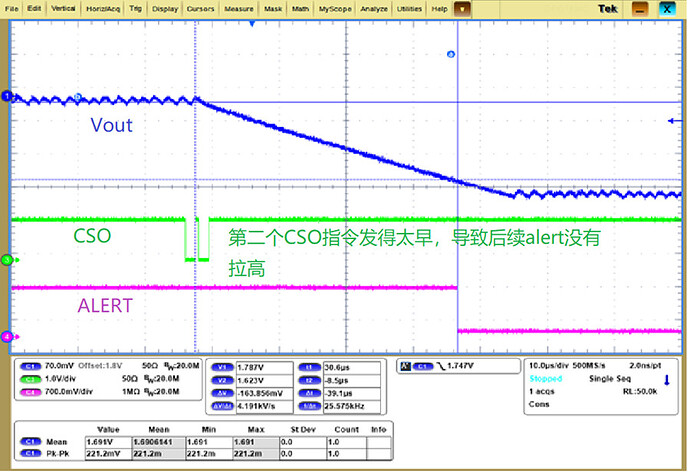

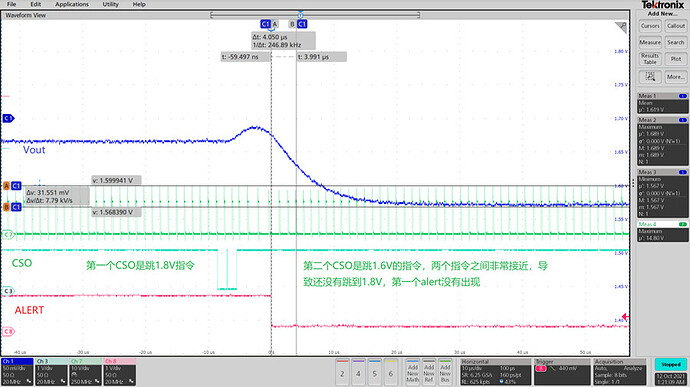

B. 服务器中CPU指令间隔时间不同的对比测试(注意CSO和ALERT波形)

但是下面这幅图可以看到只有一个alert拉低的动作,原因是在发出跳1.8V指令没过多久就立马发了跳1.6V的指令,还没来得及跳完1.8V。

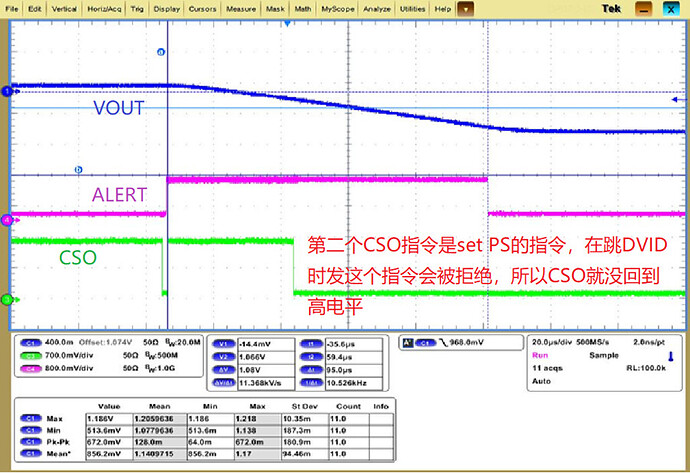

C. 补充controller拒绝CPU指令的波形(关注CSO波形)

4 个赞

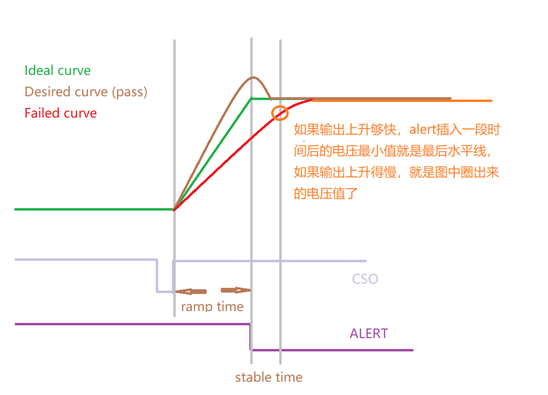

关于DVID测试中的电压波形

如果输出电容过多或者某些参数没设置好,输出电压上升的斜率过慢,导致alert插入一定时间后电压还没有调到指定值,会造成fail。下图绿色为理想状态下的DVID调压曲线,在规定的时间内(CSO上升沿到ALERT下降沿),输出电压调至了CPU需要的电压值,棕色的是我们实际测试期望的波形(controller提前几个step开始跳,让输出电压在设定时间之前先往高的跳,然后再调回稳定的电压值),红色的是fail的波形,输出调压过慢,导致在alert插入后一段时间内(这个时间测试表格会给出)都无法调至需要的电压值。

如何去改善这个上升缓慢的问题呢,有三种方法:

通过MPS的I2C工具GUI调节DVID upward,这个是让它多提前几个step调压

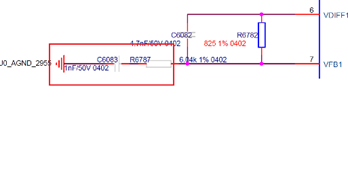

如果DVID upward已经调到最大6个step了,接下来可以调VFB1 pin脚到地的阻容参数(一般为6.04kohm,1nF,一开始没上件)

还有一个可调的就是减小输出电容,让输出电容充电更快,输出上升得也更快。

3 个赞

笔电Transient 测试波形

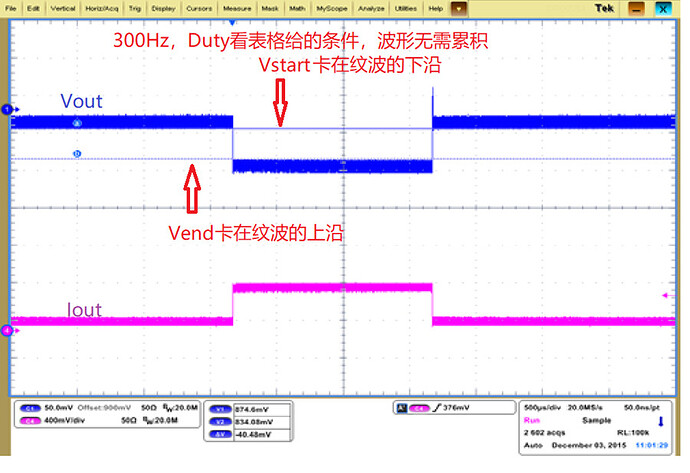

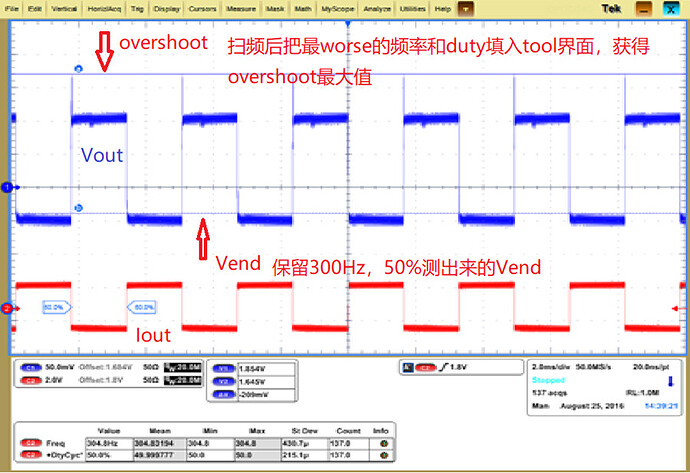

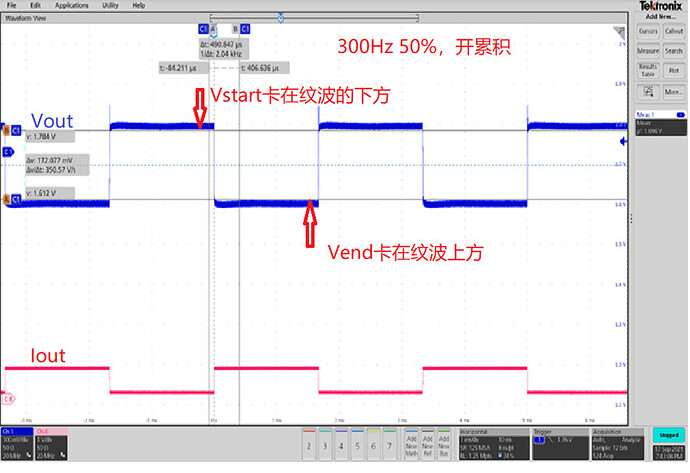

区别于普通的DCDC,我们需要先截取300Hz, 50%(看测试表格给的多少duty)的V_start以及V_end。

将V_start和V_end填入测试表,接下来就是测试最worse的overshoot和undershoot,可以通过over和under的字面意思知道,这两个一个上冲,一个下冲。

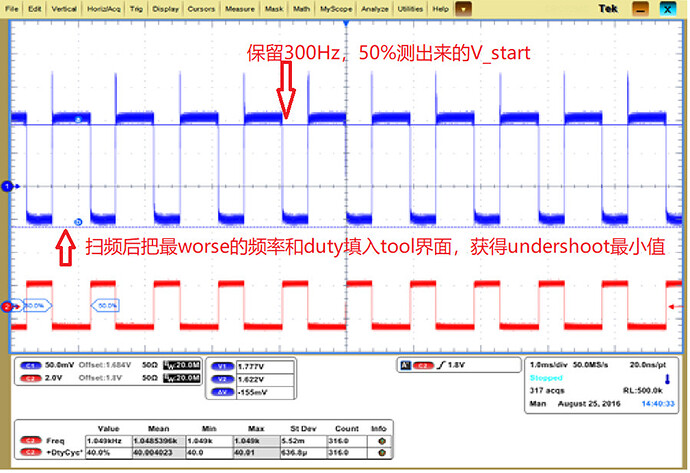

下面这幅图为笔电测试过程中的undershoot的波形。首先保留300Hz,50%测到的V_start光标,调至输出undershoot最差的频率,光标卡到undershoot并记录数值。

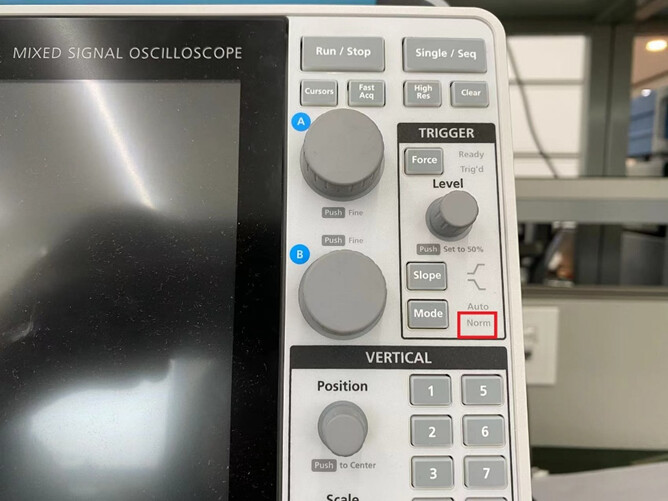

笔电测试一般是保持duty不变,改变跳载频率,这个在Intel测试工具界面上有操作的地方,一点点改变频率,从300Hz扫到1MHz,然后使用示波器上的触发功能,触发到波形后继续移动触发的电平,直到触发不到为止,这个就是最worse的点。

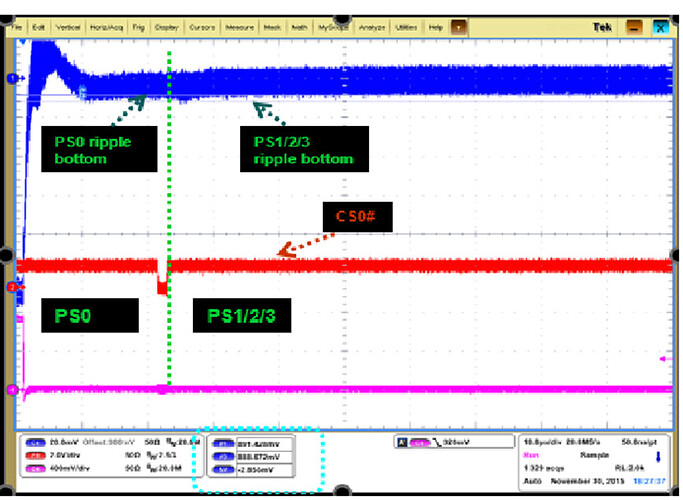

笔电测transient还有一个测试,就是在进入轻载后,需要发切PS的指令,并且测试切PS前后纹波底部的差值,如下图所示。需要注意的是,进入transient之前先把PS都设为PS0,进入之后再enable PS change,测试完成关掉transient之前把PS都改为PS0。

5 个赞

服务器VRTT transient测试波形

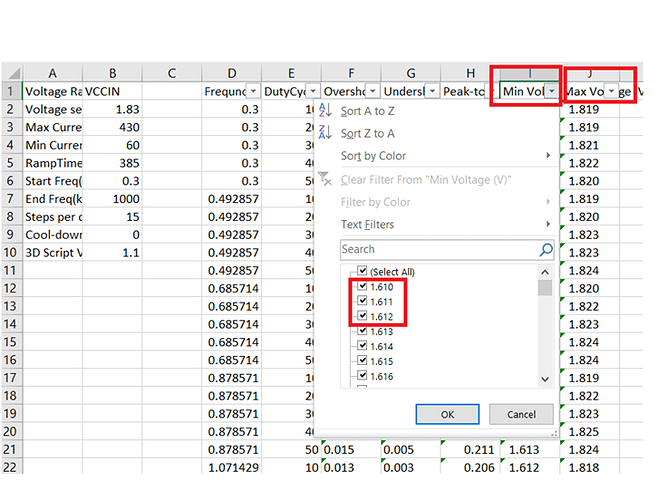

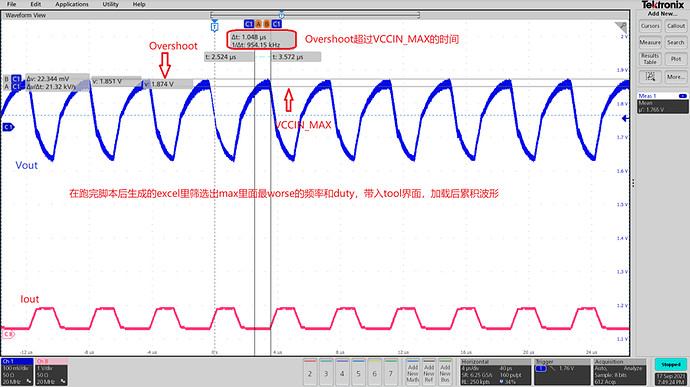

相较于笔电,服务器transient测试更加精细,除了需要从300Hz扫到1MHz,占空比也要从10%扫到90% (载重的时候是10%-50%,表格会有提示),方便的是服务器的扫频和占空比可以通过跑脚本自动扫的,然后我们可以通过脚本生成的excel表筛出最worse的点。还有一点是服务器需要开累积截取transient波形防止漏掉一些worse的点,一般要累积500次以上。

与笔电transient一致,一开始也需要卡300Hz,50%的V_start和V_end。

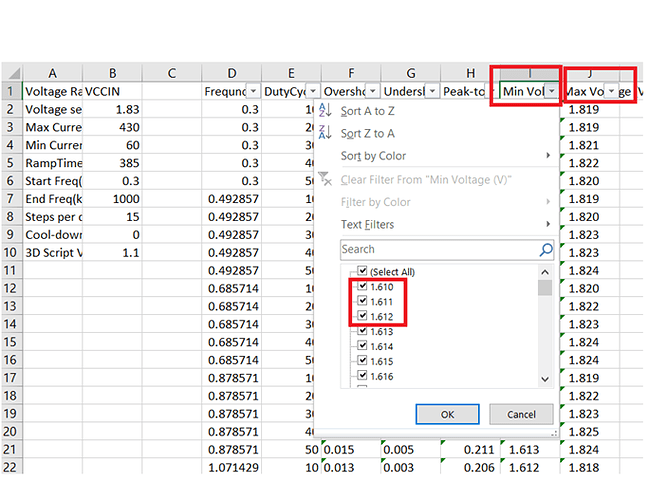

扫频脚本的修改后续会讲到,下图是扫频完成后生成的excel文件,我们可以用excel自带的筛选功能,分别在min voltage和max voltage里选出min里面的minimum和max里的maximum,把对应的频率和占空比填入测试表格,后可以将频率和占空比带入tool界面跑起来截取波形。

Undershoot测试与笔电类似,就是把扫频得到的最worse的频率和duty在tool界面设置好后,开累积截取波形,光标卡在undershoot最小值。

Overshoot测量方法也与笔电类似,就是把扫频得到的最worse的频率和duty在tool界面设置好后,开累积截取波形,光标卡在overshoot最大值。这幅图的overshoot波形不像前面的那么规整,是因为跳载频率高了,输出波形产生了畸变。

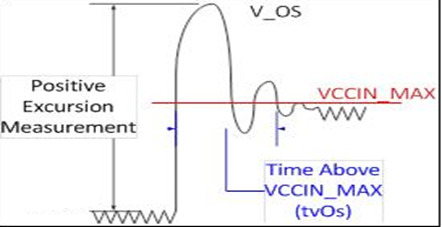

Overshoot还需要测量一个VCCIN_MAX以及overshoot超过VCCIN_MAX的时间。这个VCCIN_MAX目前不同人有不同理解。有人理解为在300Hz 50%卡纹波的上沿,有的人理解为在最worse的overshoot频率duty点,输出电压在轻载进入重载最后一个时刻纹波的上沿(如上图卡的VCCIN_MAX)。不过目前overshoot超出VCCIN_MAX的spec是25us,目前测到的overshoot最worse的频率一般大于100kHz,本身在轻载停留的时间就很短,小于25us,一般都能过spec。

服务器transient过程中PS切换的问题

5 个赞

shannon.jin:

A. 测试中常见的CSO和Alert波形解读

第二个CSO指令发送太早是否是因为在Decay down时候。我观察fast down和slow down波形时,CSO都在后段去拉高Alert

是的,因为在decay的时候,输出是不带负载,自然衰减的,时间不可控,清空alert如果早早地发送了,就没办法拉高alert,如果在笔电测试想要拖延第二个CSO的发送时间可以在SVID control界面里自行设置DVID循环并修改距离上一个指令的delay CLK;fast和slow,斜率都是固定的,电压跳变时间可以预期,清空alert的指令可以准确在alert拉低后发出,在tool上设置好DVID跳变的参数即可。

4 个赞

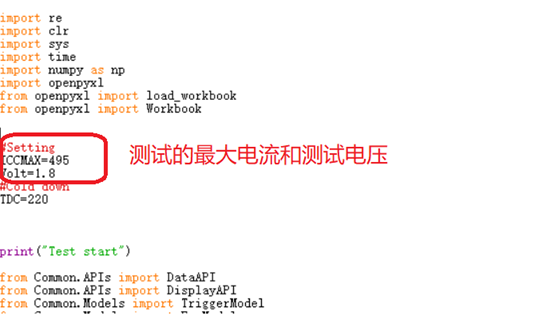

脚本测试代码修改

服务器测试的自动脚本可在FAE处获取,下面我们来看看测试脚本修改步骤吧。

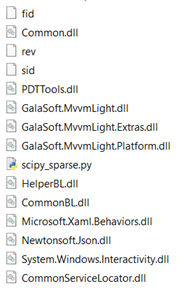

首先这些插件需要和脚本在同一文件夹下面

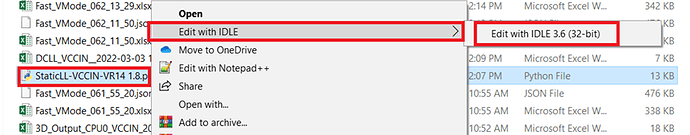

脚本修改后在run这个tag选择run module后就可以跑脚本了。运行的同时Intel的自制软件也需要开着,方便脚本控制intel软件运行。

Static LL 脚本修改

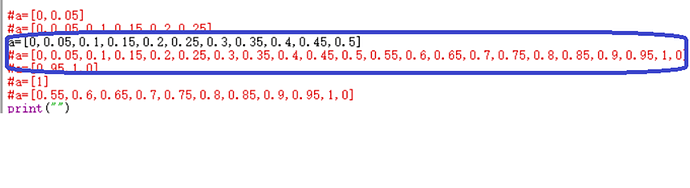

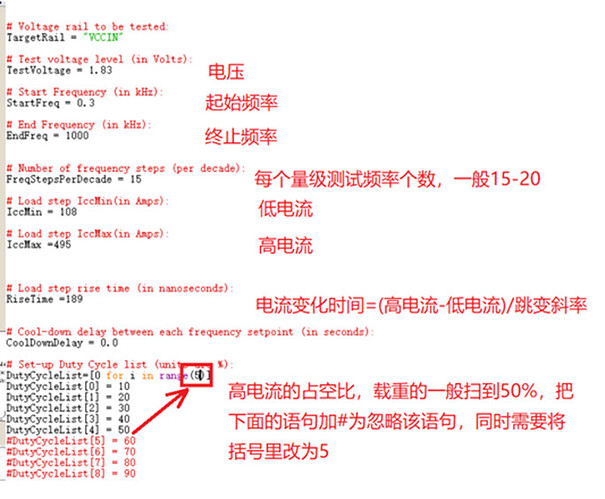

Transient 脚本设置

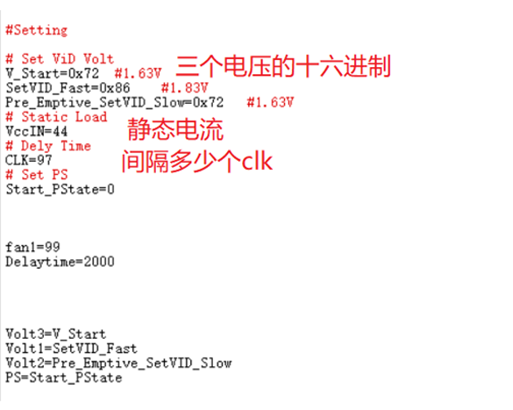

DVID 脚本设置

3 个赞

服务器软件安装

在服务器测试transient过程中,不仅需要将频率从300Hz扫到1MHz,在各个频率点还需要占空比从10%扫到90%来获取overshoot以及undershoot的数据量很大,这个扫频率和占空比的工作就由自动化脚本来代劳了。

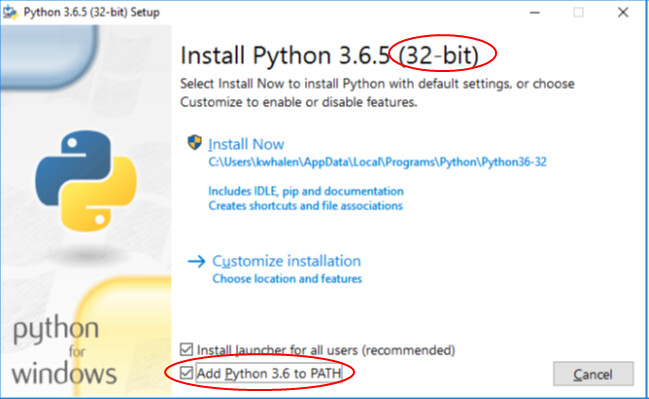

除了intel研发的测试工具,我们还需要安装python,目前测试安装的是python 3.6.5 (32位),在安装过程中需要勾选下图圈出部分add python 3.6 to path.

安装好python后需要装一些插件,打开windows的终端(WINDOWS+R然后输入CMD),界面出来后,一条条输入以下的命令按回车

pip install openpyxl

pip install numpy

pip install pythonnet

pip install pillow

pip install matplotlib

pip install pandas

pip install xlrd

4 个赞

Set WP波形解读

Set WP全称是set working point,这个测试与DVID类似,CPU发出set WP指令,输出电压完成跳变,截取CSO上升沿到alert下降沿的时间,并且测量在alert插入一段时间后,输出电压的最小值(详见DVID波形测试)。Set WP与DVID不同的是,set WP需要几个rail一起跳。

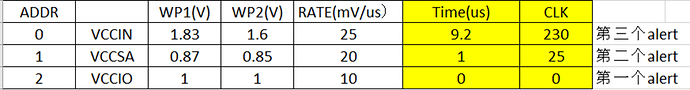

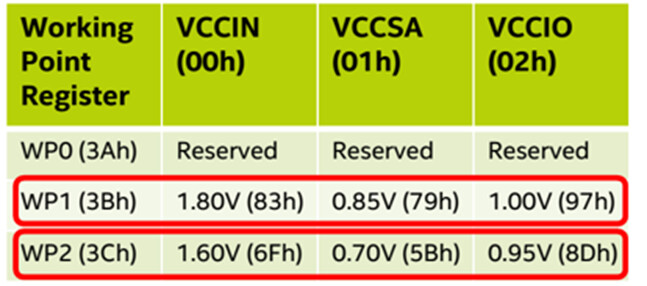

下图是VR13HC 某个测试版本set WP的测试条件,WP1里,VCCIN,VCCSA和VCCIO的电压分别为1.83V, 0.87V和1V,WP2分别为1.6V, 0.85V和1V。根据电压差和斜率计算出每一个rail电压跳变所需的时间,如下表有颜色的部分,VCCIN的time=(1.83-1.6)/0.025=9.2us,一个CLK为40ns,那么VCCIN完成电压跳变需要的CLK=9.2/0.04=230个CLK。同理可得其余两个rail完成电压跳变所需的时间。

从时间上可以看出VCCIO在接收到指令时就会马上完成跳变,紧接着VCCSA也会完成跳变,过比较长的时间后,VCCIN会完成跳变,ALERT拉低的顺序也会跟着三个rail完成跳变的顺序来。

3 个赞

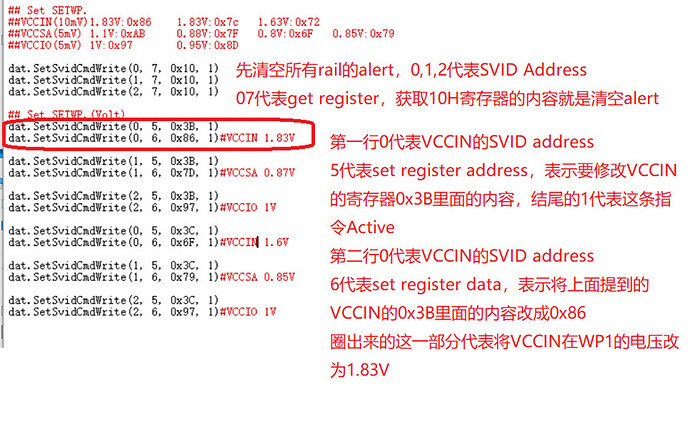

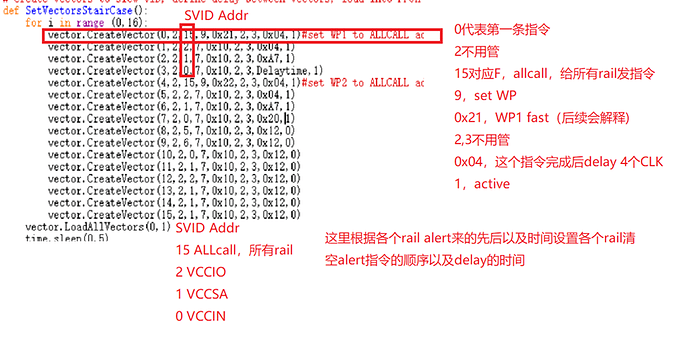

下面我们来看看set WP的脚本修改。

下图可以看到三个rail的SVID Addr,WP1和2对应的寄存器,电压的话需要根据测试表格要求修改,测试需要拿到最新的表格因为Intel一直在更新平台要求。

设好了各个rail在WP1和WP2的工作电压后,就需要修改每个清空alert指令发出的时间。

第一个是0,它代表第一条指令,可以看到每一行这个数字是递增的。

第二个是2,每一行这个数字都是一样的,不需要去改动

第三个是15,十六进制就是F,代表SVID address里的all call,是给所有rail发指令,可以看到下面的几行是2,1,0,分别代表VCCIO, VCCSA, VCCIN的SVID address,前面有讲到过这三个调压完成的顺序。

第四个是9,这个对应的就是set WP指令,下面几行7代表get register,获取寄存器数值

第五个是0x21,这个的意思是set WP1 with fast slew rate,后期会补充怎么计算这个值,后面几行0x10和上一个get register连起来就是清空alert。

第六个和第七个数字分别是2和3,这两个数字也不需要管

第八个数字是0x04,它代表的就是在这条指令完成后间隔多少个CLK去进行下一条指令

最后一位数字是1,代表这条指令active,可以看到最下面几行最后一位数字是0,代表最下面几行不工作。

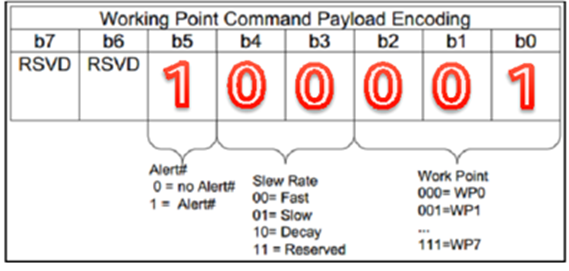

Set WP那条指令0x21以及0x22是怎么算出来的呢

Delay的CLK该怎么计算呢

VCCSA在set WP1后25个CLK就会来,但因为和VCCIO的alert太近,再加上VCCIO清空alert的CSO也有38个CLK,时间上有冲突,所以就接着VCCIO清空alert信号后4个CLK发出。

第三个alert属于VCCIN,在set WP1后230个CLK到来,时间该怎么算呢,考虑到前面两个CSO各自占38个CLK以及前面每条指令间隔4个CLK,VCCIN清空alert的指令距离上一条指令delay的时间就是230-38-38-4-4=146个CLK,也就是说在清空VCCSA alert发出后大概146个CLK后我们可以去清空VCCIN的alert,下面这个脚本选取的时间为167个CLK(16进制A7)比146个CLK(16进制92)长,长一点没问题,把alert拉高就行。

具体问题具体分析,结合表格和实际跑出的波形,可以适当去修改delay的CLK。

5 个赞