01

攻克目标1:暗中搅局的的变压器寄生电容

我们知道,EMI由差模+共模构成。差模噪声回荡于L-N线;共模噪声则游走于寄生电容到地之间。在反激变换器中,共模较之差模更凶险。变压器原副边之间分布着许多寄生电容,原边MOS管漏极对地同样存在寄生电容,两者共同作用,为共模电流独辟蹊径。由于反激变换器定位的功率较小,与之匹配的MOS的寄生电容作用相对削弱,由此变压器寄生电容对共模噪声的影响便更为突出。

攻克目标2:Y电容的前世今生

Y电容的作用即是把通过变压器寄生电容流入副边的共模电流旁路回原边,以阻止该共模电流流经对地阻抗后回归至交流侧,从而达到减小EMI的目的。然而Y电容亦是一把双刃剑,一旦其发生失效,交流侧的电流则会漏入副边,存在极大的安全隐患。为保证设计可靠,通常会串联两只Y电容作冗余,而这与当前业界不断追求产品小型化的趋势又相斥。

如何减少抑制共模噪声的滤波器,如何在Y电容缺席的前提下保证EMI顺利通关,成败皆在变压器。就让我们细细品读王硕教授潜心研究的反激变压器设计之道。

02

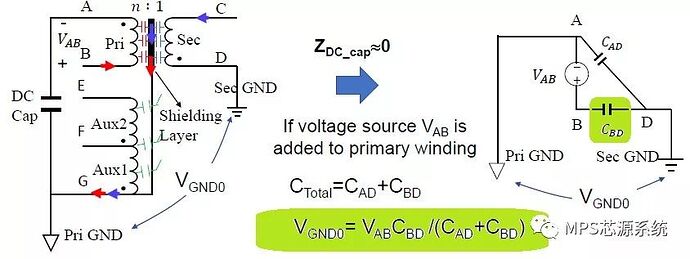

任何科学的研究离不开数学建模的支持,王硕教授及其团队将复杂的反激变压器共模模型简化为两个电容模型的架构,以便分析EMI共模噪声的抑制。由于原副边地之间存在等效阻抗,一旦原副边地之间的压差VGND0建立,便形成了共模电流,目标很明确:如果能将VGND0降至最低,即可有效抑制共模噪音。如下图,假设原边绕组的端口AB之间施加一电压VAB,故VGND0的大小则取决于等效电容CBD的容值。目标进一步明确:CBD容值越小,共模噪音越低。

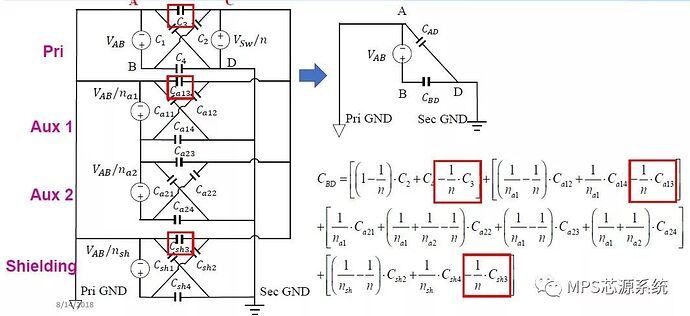

CBD由哪些因子组成呢?变压器各绕组端口之间均存在寄生电容,排列组合后会形成繁琐庞大的数学模型(如下图),而对于应用端的工程师而言,只需了解最终影响CBD的关键参数即可。在这个公式中,我们可以看到三项负数因子,其分别对应图中红框所示的电容,称之为平衡电容,通过增减这些容值,使其正负抵消,最终获得CBD=0。

这里穿插一个Tips:如何在实验室验证变压器的性能?

根据上述分析可知,任何反激变换器的多绕组变压器可以等效为一个CBD+CAD的电容模型,我们知道想要降低共模噪声,CBD越小效果越佳。如何利用常规的实验仪器就能检验变压器性能的优劣呢?王硕教授在此支招:

将信号发生器施加电压至AB端,用示波器分别测得AB之间的电压与原副边两地之间的电压,两者相比后,比值越小,说明该变压器的CBD越小,共模噪声则越低。

03

在实际电路中,除了变压器各绕组之间寄生电容引发的噪声以外,还有一只潜伏的寄生电容大军遍布各处,即变压器的磁芯与绕组之间,磁芯与各功率管的散热器之间,气隙导致线圈与散热器之间,均存在寄生电容,即便能将CBD降为0,而这些寄生电容诱发的噪声耦合,同样会影响EMI测试的结果。基于此,王硕教授进一步提出:

解决变压器外部寄生电容的共模噪声的方法:

磁芯接地:可以将原边至磁芯的共模噪声旁路回原边。

铜箔包裹磁芯后接地:可以屏蔽绕组与功率管散热器之间的耦合路径,将共模噪声旁路回原边,一举斩获所有原边至副边的耦合噪声。

副边绕组居中绕制:将原边绕组或辅助绕组分别靠近磁芯中柱与两侧绕制,副边绕组居中,使得其远离磁芯,从而降低副边与磁芯的耦合。

中场总结

降低反激变换器共模噪声的有效途径:施加平衡电容+磁芯屏蔽。各个击破,将干扰降至最低,用科学的手段省去耗成本耗体积的共模滤波器。

04

解决了开篇提出的问题一,对于Y电容如何规避呢?细心的读者会发问:平衡电容需要跨接于原副边绕组之间,这和Y电容的性质是相似的。如何才能完全将Y电容取缔呢?同样从变压器出发,王硕教授巧妙提出:

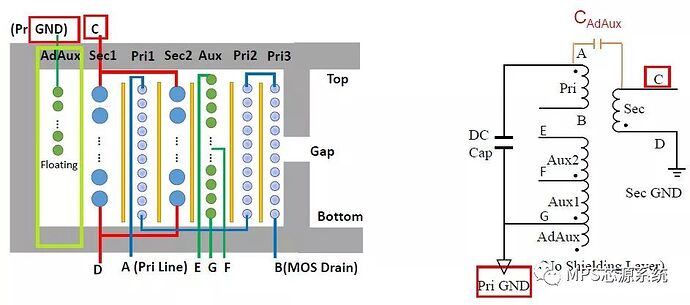

在靠近副边绕组的动点处增加一层辅助绕组,该绕组一端接原边地,一端悬空,绕组的匝数对等于Y电容的容值,从而起到将副边共模噪声旁路回原边的目的。

05

介绍了反激变压器EMI的优化设计之余,王硕教授还与工程师们分享了电机驱动系统中共模噪声的抑制方法,同样通过数学建模,基于低损耗小尺寸的正馈电流注入有源滤波器,混合不同的无源滤波器,阐述EMI测试的结果。

同时,MPS市场技术及应用工程师经理——罗钲,介绍了MPS芯片在设计和应用中的几个技巧来消除EMI:

- 封装上通过MESH CONNECT的技术减小寄生电感来降噪;

- 输入电容采用对称性布置 从而设计出相反的磁场来抵消总磁场;

- 还有把对噪声影响很大的输入电容集成于芯片内部的技术。