EMC (Electromagnetic Compatibility) 为电磁兼容,包含了EMI (Electromagnetic Interference) 和EMS (Electromagnetic Susceptibility) 两个方面的含义。其中EMI为电磁干扰,考量的是电子系统对外发射电磁波的特性,对外发射的电磁波通常会对其他设备造成干扰;EMS为电磁敏感度,考量的是电子系统对电磁干扰的敏感程度。

在电子系统中,DCDC变换器通常是潜在的EMC噪声源,因此必须重视开关电源的布局规划、选型优化以及模块内layout。

1.1 方案设计

1.1.1 布局规划

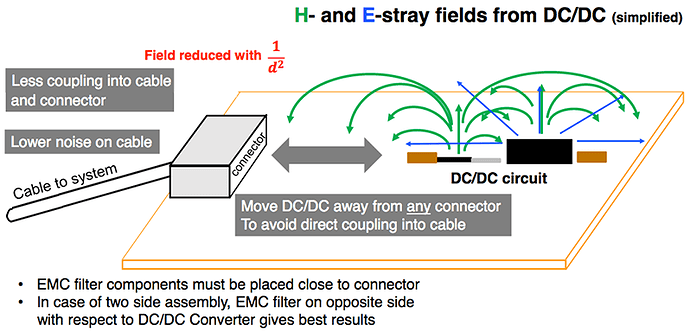

为避免将DCDC变换器中的电场磁场耦合进连接器和电缆,变换器需要尽远离连接器以及线缆。DCDC变换器也应当避免放置在PCB边缘,否则不利于用PCB屏蔽变换器产生的电磁场。

EMC滤波器元件应当尽可能靠近连接器放置。

如果成本允许,对DCDC模块整体覆盖屏蔽罩能够阻断EMI路径,极大地改善EMI性能。

1.1.2 降低开关频率和开关速度

DCDC变换器的噪声辐射水平与开关频率和开关速度有直接联系,更低的开关频率和开关速度有助于降低变换器噪声辐射水平。但是需要注意,开关速率的降低意味着变换器需要使用更大的电感电容来进行输出滤波,变换器的PCB面积以及BOM成本会提升。而开关速度的降低会增加MOSFET的开关损耗,意味着变换器的效率将降低。

1.1.3 在输入和输出线路上使用电感或者磁珠

在输入输出线路上使用电感或者磁珠可以有效地阻止DCDC变换器开关噪声传播。

1.1.4 在输入和输出线路上使用组合电容

在输入输出线路上使用不同尺寸和容值的低ESR MLCC电容,对关心的频带形成充分的滤波。小尺寸的0402/0201的22nF~100nF电容可以很好地阻止来自于开关节点的高频噪声耦合到输入输出外部。特殊封装的0204电容等具备更小的ESR,更适用于该应用场景。

1.1.5 Cboot电容上增加串联电阻

对于Buck变换器,上管需要浮地驱动,该驱动器的供电来自于自举电容Cboot。在集成的Buck转换器中,Cboot由内部的稳压器进行供电,其电压通常为4V~5V。

通过降低上管开关的导通速度可使Buck转换器开关波形和电流脉冲的上升时间增加,这可通过给Cboot增加一只串联电阻Rboot来实现。

注意,开关速度的降低将增加Buck变换器的开关损耗,进而降低效率。Rboot的值一般为5-10Ω,对于高占空比应用,取值需要进一步降低,以保证对Cboot充分充电。

1.2 选型优化

1.2.1 频谱展开功能

部分芯片带有频谱展开功能,即通过频率抖动功能,将集中在开关频率及其倍频处的能量分散到以开关频率为中心的具有一定宽度的频段内,进而有效降低了每个频点的噪声赋值。

1.2.2 同步型方案

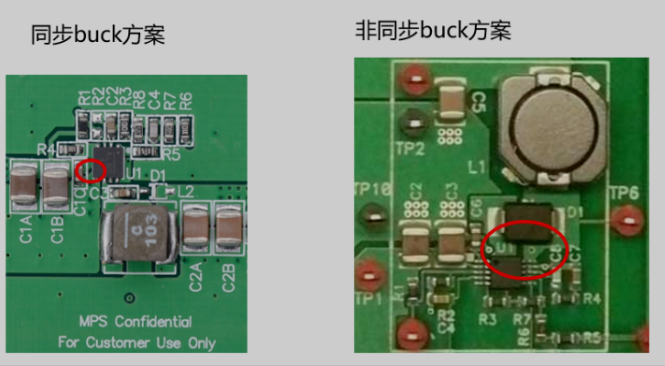

相比于非同步方案,同步型方案使用内部集成MOS,无需外部二极管,因此具备更紧凑的PCB布局,power stage也具备更小的高频环路面积,因此EMI效果更好,如图2所示。

1.2.3 片内集成bypass电容

为了获得更小的高频环路,有些芯片内部集成了bypass电容,这将极大地改善EMI性能。

1.2.4 片内集成功率电感

与片内集成bypass电容原理一样,部分电源模块将功率电感集成,可以获得更小的高频环路以改善EMI性能。

1.3 Layout

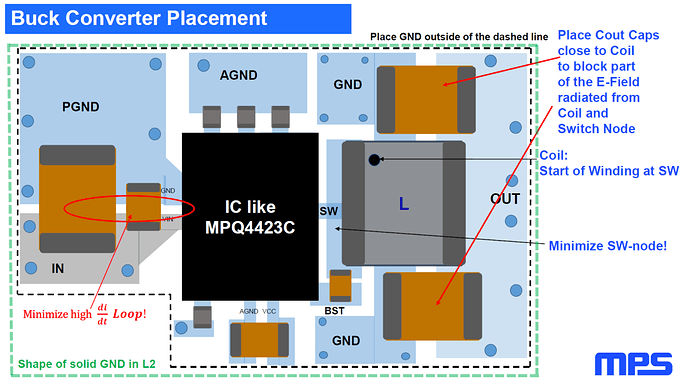

1.3.1 最小化di/dt和dv/dt环路

如图3所示,buck的power stage可以看作输入输出两个重要环路:输入电容、集成在buck芯片中的high-side MOS、电感、输出电容构成的充电过程环路,以及集成在buck芯片中的low-side MOS、电感、输出电容构成的放电过程环路。其中,最重要就是由输入电容,high-side MOS和low-side MOS组成的高频电流环,应保证环路面积尽可能地小。

综合以上考量,应该遵循如下原则:

- 输入电容应当尽可能靠近buck芯片,电容到芯片的VIN与GND应该采用短而粗的走线,最大化降低走线的ESR/ESL。如果具备多种类型的输入电容,则小尺寸低容值的高频滤波电容应该更靠近芯片;

- 电感尽可能靠近SW引脚,SW走线应该短而粗;

- 输出电容尽可能靠近电感;

- Power stage所连接的GND应该具备完整平面,各个元件接地应该具备足够多的过孔以最小化DCR以及DCL;

- 在变换器布局周围,同层放置GND敷铜对电源噪声进行屏蔽;

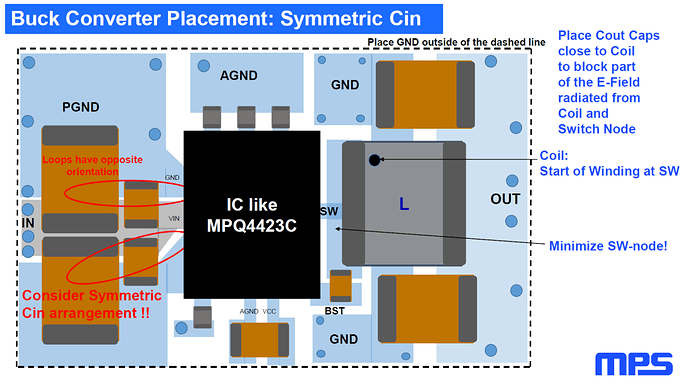

1.3.2 对称放置输入/输出电容以抵消磁场

如图4所示,将输入/输出电容对称放置,则其

电流产生的磁场方向相反,则会互相抵消,即可以有效改善EMI性能。

1.3.3 输入和输出电容尽可能靠近高频环路

输入和输出电容,应该尽可能靠近di/dt和dv/dt环路,输入和输出电容的电源端应当分别靠近芯片电源输入以及电感输出,走线尽量短而粗以降低走线的ESR和ESL。

1.3.4 使用多层PCB

使用4层及以上PCB,确保电源层下有完整的地平面。同时,电源层也应该在DCDC变换器周围部署地平面进行屏蔽。

1.3.5 使用屏蔽罩

使用屏蔽罩,可以良好地屏蔽变换器噪声,但是会提高系统成本。

参考文献

- MPS视频 20220412 直播回顾:揭开 DC/DC EMI 中 Layout 的 “神秘面纱”

- Influence of Layout on EMI performance of Buck-Boost Converters, Brigitte Hauke, Texas Instrument

- Reducing EMI in buck converters, Richtek