简介

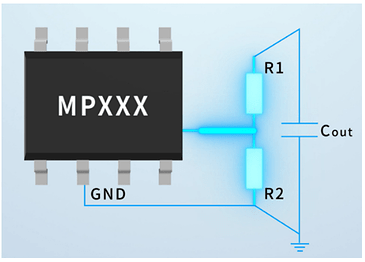

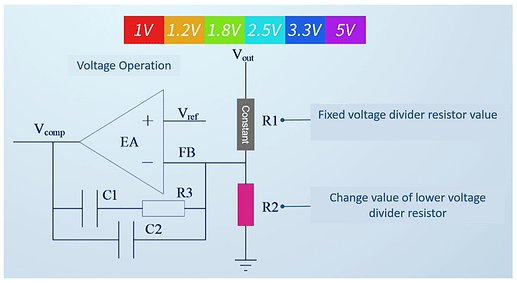

在 DC/DC 变换器中,反馈 (FB) 分压电阻的规格常给设计人员带来各种设计挑战,例如如何确定所需的电阻或调节参数(如输出电压、上分压电阻或下分压电阻)。 图 1 显示了 FB 上/下分压电阻的各种幅度组合。

图 1:FB 上/下分压电阻的各种幅度组合

本文将探讨 FB 分压电阻的设计规范,包括待机功耗、输出电压精度和环路特性。

待机功耗

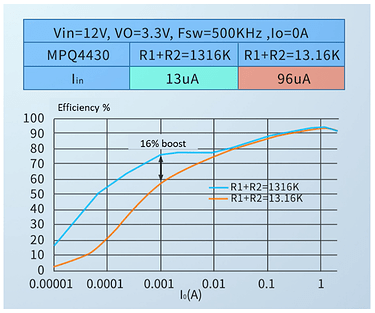

图 2 显示了具有低静态电流 (IQ) 的 DC/DC 变换器,其 FB 分压电阻在不同数量级下带来的效率差异。以 MPQ4430 为例,R1 和 R2 是其分压电阻。

图 2:R1 和 R2 数量级不同带来的效率差异

优化待机功耗,尤其是对电池供电产品,可以按比例增大 DC/DC 变换器的 FB 分压电阻值。

输出电压精度

增大 FB 分压电阻的阻值,可以降低待机功耗。

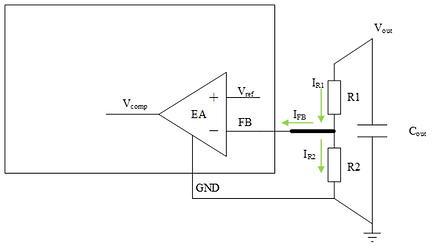

FB 是运算放大器(op amp)的负输入端,它会汲取一定的电流。当 FB 电流(IFB)在分压网络中占比较小时,IFB 可忽略不计;当其占比较大,即分压电阻选值较大时,IFB 就不容忽视(见图 3)。

图 3:FB 电流在分压网络中的占比

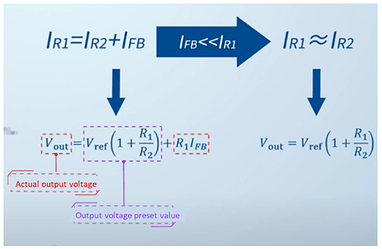

如图 4 所示,当实际输出电压 (VOUT) 由于 IFB 的存在而超过预设值时,会降低电压精度。

图 4:计算输出电压精度

因此,建议选择合适的阻值,使流经分压电阻的电流超过 IFB 的 50 倍。

环路特性

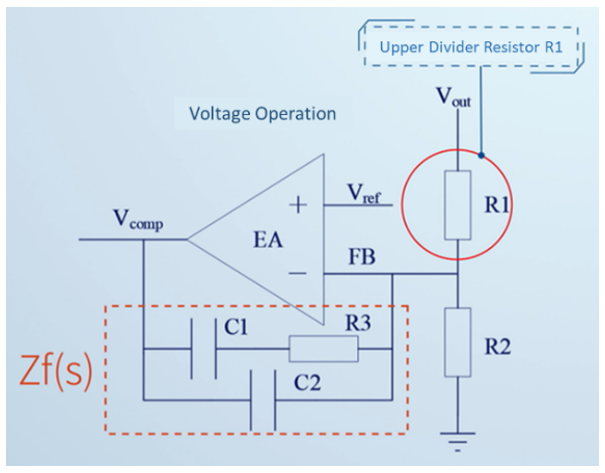

FB 电阻还会影响芯片内部的环路特性。当反馈网络只是单电阻的情况时,电压型运放,误差放大器增益与上分压电阻 R1 有关,在动态负载对纹波有要求的场景,我们可以调整 R1 阻值做进一步优化。

图5: 电压模式运放

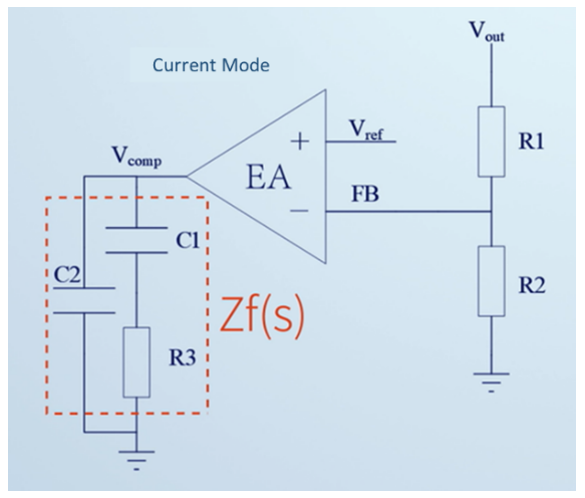

在电流模式运放中,运放增益 (GEA(S)) 与 R1 / R2 值没有直接关系,但与两个电阻的比值有关。图 6 所示为电流模式运放。

图 6:电流模式运放

对于不同的 VOUT 场景(1V、1.2V、1.8V、2.5V、3.3V 或 5V),建议保持上分压电阻的阻值不变,只调节下分压电阻的阻值,以获得近似的环路特性(见图 7)。

图 7:根据输出电压的不同调整下分压电阻的阻值

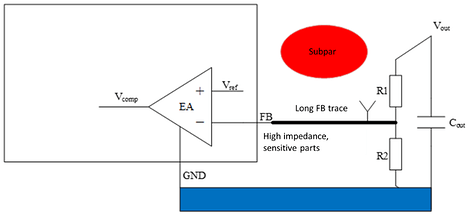

确定 FB 分压电阻值后,还需要注意 FB 引脚的接线。FB 是容易耦合噪声的高阻抗引脚。在实际应用中,常见到 R1、R2 放在输出电容端,这导致 FB 走线较长。这段 FB 走线充当了天线,更易耦合非实反馈,继而导致 VOUT 变化或不稳(见图 8)。

图 8:长 FB 走线更易耦合非实反馈

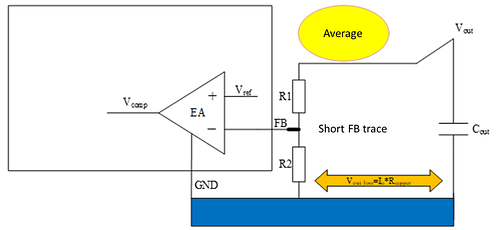

在电路布线设计中,FB 走线应尽量短,R1、R2 应尽量靠近 IC 的 FB 引脚放置;但 VOUT 输出直流电平,抗干扰能力强,所以可采用长走线(图 9)。

图 9:电路走线中的短 FB 走线

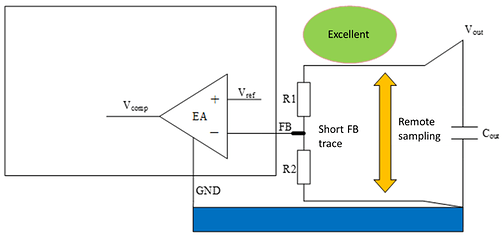

一般在输出电流(IOUT)只有几个安培时,R2 的接地可以靠近芯片地。但当 IOUT 超过 10A 时,由于接地线上的敷铜有限,地线上的电压会损失,导致实际 VOUT 低于预设电压。在这种情况下,建议使用远程采样(见图 10)。

图10:远程采样/p>

结语

要优化 DC/DC 变换器 中 FB 分压电阻的 FB 布线,首先要保持第一个电阻走线尽可能地短,并在同一侧直接连接第二个电阻。同时确保没有干扰源,如开关、电感、噪声地等。

要了解更多详细信息,请浏览 MPS 官网上提供的各种开关变换器和控制器信息。

查看更多技术资源可访问: Resource Center (monolithicpower.cn)