PG引脚我如何连接。

问题1:VIN=5V,Vout=3.3V PG引脚我需要如何连接,看datasheet有如下一段话,我的理解:因FB电压为0.6V,调节电压为Vout=3.3V,那么0.6超出了3.3的10%,所以PG应该连接到LG吗?

“MPM3840 使用集成了一个 500kΩ 上拉电阻的开

漏作为电源正常输出指示(PG)。

当 FB 电压为调节电压的 10% 之内时,PG 上拉

至 VIN;否则,PG 拉低。当 VFB 达到 PG 阈值

到PG 置高时, 会存在一个140μs 的延时。

MOSFET 最大导通阻抗(RDS(ON))为 100Ω。”

问题2:DATASHEET中P4页表格中关于PG的说明不理解,拜托详细解释下

(1)电源正常输出指示欠压(PG UV)上升阈值

(2)电源正常输出指示欠压(PG UV)下降阈值

(3)电源正常输出指示过压(PG OV)上升阈值

(4)电源正常输出指示过压(PG OV)下降阈值

(5)电源正常输出指示(PG)延时

(6)电源正常输出指示(PG)逻辑-高电压

您好,

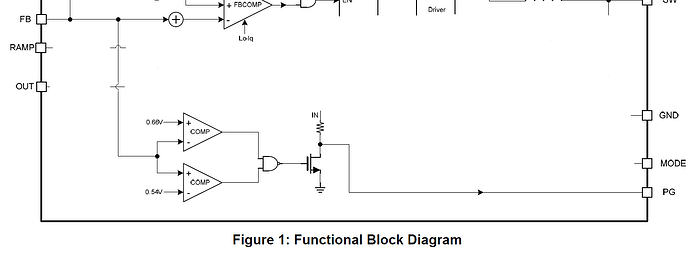

PG(Power Good)是对外指示芯片输出良好的引脚,内部为开漏结构。当FB电压(VOUT分压而来)超出可接受范围时,PG改变其状态(由关闭变为开通),其在内部方框图中的位置如下:

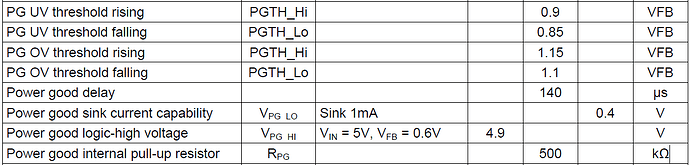

上拉电平和判断阈值在数据表中可以找到:

相应的:

- MPM3840的PG开漏结构在内部存在500kΩ上拉,PG良好的状态为高电平,超出范围时转为低电平

- UV(Under voltage) threshold rising 欠压上升阈值,是指当输出欠压后,输出电压上升时,PG从Bad转化为Good的条件

- UV(Under voltage) threshold falling 欠压下降阈值,是指当输出即将欠压,输出电压下降时,PG从Good转化为Bad的条件

- OV(Over voltage) threshold rising 过压上升阈值,是指当输出即将过压,输出电压上升时,PG从Good转化为Bad的条件

- OV(Over voltage) threshold falling 过压下降阈值,是指当输出过压后,输出电压下降时,PG从Bad转化为Good的条件

6.欠压和过压都有上升和下降阈值,是为了构建一个滞回窗口,避免单一阈值引起的震荡 - Power good delay为触发相应阈值到PG电平发生改变的延时

- Power good logic-high voltage是PG引脚两种状态相应的电平,PG通常供后级电源使用,需要考虑电平兼容等问题

谢谢回复,PG引脚是不是也可以悬空?

同时请教小SW引脚的功能是什么?可以悬空吗?

您好,PG不使用的话可以悬空。对于集成电感的电源模块,SW引脚预留一般是为了测试以及散热,MPM3840的SW引脚均可以悬空