摘要

非稳压反激式变换器和推挽式变换器常被用于隔离式栅极驱动器电源应用,因为这类应用需要紧密耦合的变压器来降低漏感带来的损耗。现代高功率系统的开关节点通常具有较高的总线电压 (VBUS) 和 dV/dt,其变压器设计需要更高的隔离电压 (VISOLATION) 额定值和更低的绕组间电容;但这些却无法在紧密耦合的变压器上实现。

谐振拓扑是解决这个问题的理想解决方案。它利用了电感泄漏,从而允许松散耦合的变压器。谐振拓扑不仅能够降低绕组间电容、减小变压器尺寸,同时还具有高效率和出色的负载调整率。

本应用说明为您提供详尽的低成本 LLC 变换器设计指南。这种LLC变换器专为 IGBT 和 Si/SiC MOSFET 器件中的隔离式栅极驱动器设计,非常适合汽车和工业应用,包括电动汽车电机驱动器、车载充电器和并网逆变器。

简介

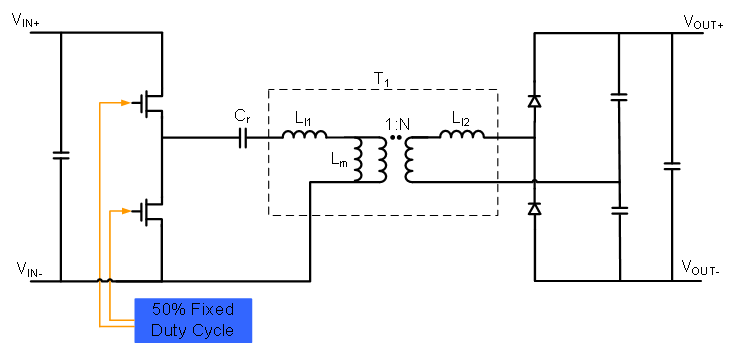

半桥原边 MOSFET 和半桥副边整流器是低功率应用的首选,因为它们需要的开关和二极管更少。LLC 变换器的设计中包含了变压器 (T1)、励磁电感 (Lm)和漏感(Ll1, Ll2)。谐振电容(Cr) 与漏感形成了 LC 谐振回路。选择与谐振回路频率(fr)差不多的开关频率(fSW)可使谐振回路阻抗保持在大约0Ω。当 LLC 变换器的转换比等于变压器匝数比(T1的1:N)时,LLC 变换器可作为直流变压器运行。根据经验,只要 Lm >10倍的 Ll1,该陈述就成立。当Lm 与 Ll1相当时,转换比超过变压器匝数比 (N) ,为

图 1 显示了这种LLC 拓扑方案。

图1: LLC拓扑方案

1. 采用 LLC 拓扑的 MPS 栅极驱动电源解决方案

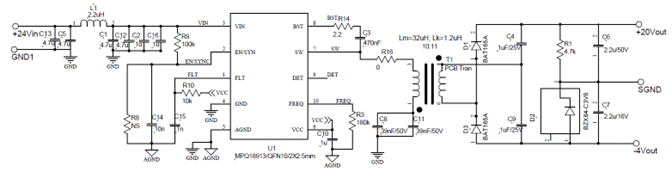

本文介绍的LLC 变换器设计采用 MPQ18913 作为半桥变压器驱动器。MPQ18913 具有高 fSW 和宽输入电压 (VIN) 范围,可实现系统设计的灵活性。图 2 显示了SiC 器件的栅极驱动器电源设计原理图。

图 2:SiC 器件的栅极驱动器电源设计原理图

如上图所示,齐纳二极管将输出电压 (VOUT) 分为两个电源轨,可用于 IGBT 或 SiC 驱动器。

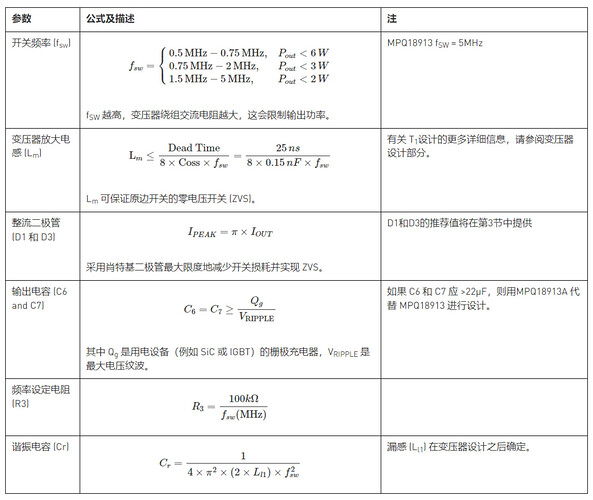

采用MPQ18913 实现 LLC 变换器时的组件选择和相关公式如表1所列。

表 1:LLC 变换器的设计公式和组件选择

2. 变压器设计

变压器的关键规格参数包括励磁电感、功耗、隔离电压 (VISOLATION) 额定值和耦合电容。建议采用两种类型的变压器,环形变压器和平面变压器。这两种电感都易于设计且耦合电容

2.1. 磁芯选择

为了充分利用 MPQ18913 的高 fSW,磁芯应该能够在高频下运行。芯材应具有较低的相对磁导率(在100 至 1000 之间)。 芯材选择示例:P9L(0.5MHz至1.5MHz,由Encore制造)、PC50(1MHz至2MHz,由TDK制造)和61 material(≥2MHz,由Fair-Rite制造)。

2.2. 环形变压器

请遵循以下指南来设置环形变压器:

1. 选择环形变压器匝数比。

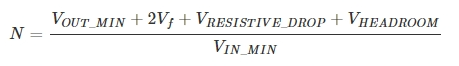

在谐振频率 (fr)下,LLC 变换器电压增益等于变压器匝数比 (N),匝数比可通过公式 (7) 计算:

其中,VF 是整流二极管(D1 和 D3)的压降,VRESISTIVE_DROP 是原边 MOSFET和变压器绕组电阻间的压降,VOUT_MIN 是 VOUT的下限,VIN_MIN 是最小 VIN, VHEADROOM 是由虚拟负载(例如 R1功耗或+20VOUT和-4VOUT之间连接的额外电阻负载)引起的VOUT 压降。

注意,VRESISTIVE_DROP 与负载电流 (ILOAD)成正比,它对栅极驱动器电源的负载调整率非常关键。为优化负载调整率,建议采用最小匝数 (N) 以降低变压器绕组的电阻。

(2VF + VRESISTIVE_DROP) 可以通过公式 (8) 来估算:

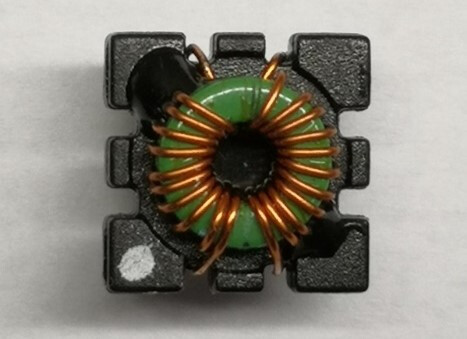

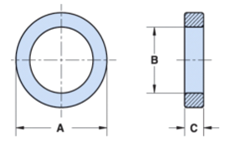

图 3 显示了一个环形变压器。

图3: 环形变压器

2. 选择窗口大小

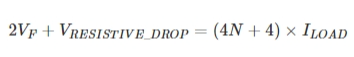

请谨慎选择环形变压器的窗口大小以适应绕组。在给定匝数的条件下,漆包线的直径可以用公式(9)来计算:

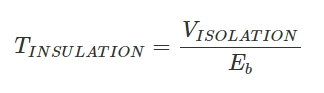

其中DTOTAL 是绕组线直径,DCONDUCTOR 是导体直径,TINSULATION 是绝缘层的厚度。

DCONDUCTOR 可以是 fSW趋肤深度的四倍。 TINSULATION与 VISOLATION 额定值相关。如果所需的VISOLATION 低于2kV,则选择击穿电压 (VBREAK) 超过变压器 TINSULATION 额定值的漆包线;如果所需的 VISOLATION 超过 2kV,则建议使用双层或三层绝缘线。如果匝数比 (N) 不等于 1,则在绕组的低压侧使用较厚的绝缘层。两侧的 VBREAK 应等于 VISOLATION的两倍。

图 4 显示了环形磁芯的几何结构。

图4: 环形磁芯的几何结构

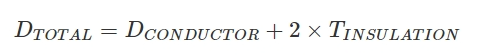

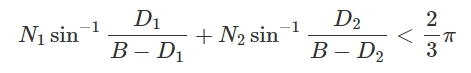

环形磁芯的内径 (B) 必须适合绕组。B可通过公式(10)计算:

其中 N1 和 N2 是匝数,D1 和 D2 是线径。

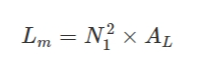

3. 根据每平方匝电感 (AL) 和磁芯损耗选择磁芯尺寸。

AL 可通过公式(11)来计算:

其中 Lm 是变压器放大电感,可通过公式2来计算(见表1)。另外两个几何参数(A 和 C)可以根据 AL进行选择。

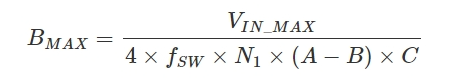

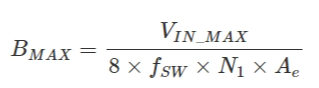

最大磁通密度 (BMAX) 可以确认磁芯损耗是否可接受。BMAX 的计算公式(12)如下:

我们需要考虑 fSW 和 BMAX处的磁芯损耗密度(由磁芯材料供应商提供)。为保证散热性能,磁芯损耗密度不应超过 150mW/cm3 。如果应用要求密度超过 150mW/cm3,则需要选择有效面积更大或匝数更多的磁芯。

4. 选择变压器骨架。

变压器骨架的选择必须适合磁芯和绕组。变压器骨架尺寸和原边与副边引线之间的爬电距离非常重要。对于 3kV 隔离电压额定值来说,建议爬电距离 ≥3.5mm;对于 5kV 隔离电压额定值,建议爬电距离 ≥7mm。

变压器构建好之后,可短接副边的两个端子,在原边测量漏感,然后通过公式 6 计算出谐振电容(参见表 1)。

2.3 平面变压器

请遵循以下指南来设置平面变压器:

1. 选择平面变压器匝数比。

平面变压器匝数比的确定方法与环形变压器相同。请参照环形变压器部分的步骤 1 确定平面变压器的匝数比。

图 5 显示了一个具有ER 磁芯的平面变压器。

2. 选择窗口大小。

如果采用的是6层PCB布局,则利用中间层形成原边和副边,如下所示:

- 用线圈串联连接中间层1 和中间层2 ,以形成原边。

- 用线圈串联连接中间层3 和中间层4 ,以形成副边。

不要在顶层和底层连接线圈,以免因耐压击穿而遮蔽磁芯。

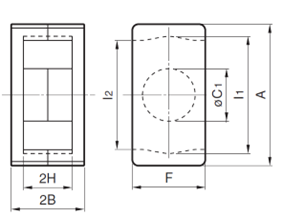

图 6 显示了ER 磁芯的几何结构。

图6: ER 磁芯的几何结构

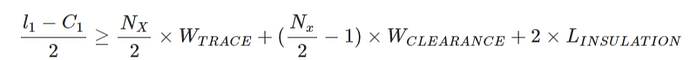

窗口大小 (l1 - C1) 可通过公式 (13) 来计算:

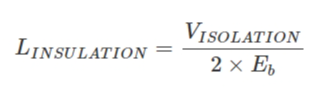

其中 NX 是原边/副边的匝数,WTRACE 是 PCB 走线宽度(1oz PCB 上,0.25负载走线宽度为10mil),WCLEARANCE 是两个 PCB 走线之间的间隙(1oz PCB 通常要求 ≥4mil 的间隙),LINSULATION 是 PCB 走线与磁芯之间的间隙。

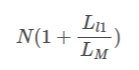

LINSULATION 可通过公式(14)来计算:

其中 Eb 是预浸材料的介电强度。

原/副边之间各个方向的间隙都可通过公式(15)来计算:

对于典型的 PCB 布局,介电强度应为 250V/mil。

3. 确定每平方匝电感 (AL)。

最佳 AL 可通过公式 11 或公式 2 来计算(参见表 1)。如果所选磁芯材料的磁导率较高,则需要有气隙来降低 AL。图 7 显示了带气隙的 ER 磁芯。

图7: 带气隙的 ER 磁芯

4. 选择磁芯尺寸。

磁芯的内部高度(2H)应根据PCB总厚度来选择。然后再选择适合 PCB 和线圈的磁芯。

通过 BMAX 可以确认磁芯损耗是否可以接受。 BMAX 的计算公式(16)如下:

我们需要考虑 fSW 和 BMAX处的磁芯损耗密度(由磁芯材料供应商提供)。为保证散热性能,磁芯损耗密度不应超过 200mW/cm3 。如果应用要求密度超过 200mW/cm3,则需要选择有效面积更大或匝数更多的磁芯。

变压器构建好之后,可短接副边的两个端子,在原边测量漏感,然后通过公式 6 计算出谐振电容(参见表 1)。

3. 选择整流二极管

二极管电容 (CT) 和反向电流 (IR) 是整流二极管的两个重要参数。这两个参数对负载调整率会产生负面影响。

CT 是 LLC 谐振网络的一部分,它可以提高 LLC 变换器在轻载时的增益。建议采用较小的 CT 以改善负载调整率。

IR 会随着二极管温度的升高而增加。在重载条件下,二极管温度升高,IR 会给 LLC 变换器增加额外的负载,从而增大负载调整率。

考虑到这些因素,建议整流二极管采用BAT165(40V,0.75A,AEC-Q101)或PMEG6010CEJ(60V,1A,AEC-Q101)。

如有相关需求可点击 MPS NOW 在线技术支持 , 工程师将为您直接提供项目技术支持服务

查看更多技术资源可访问:Resource Center