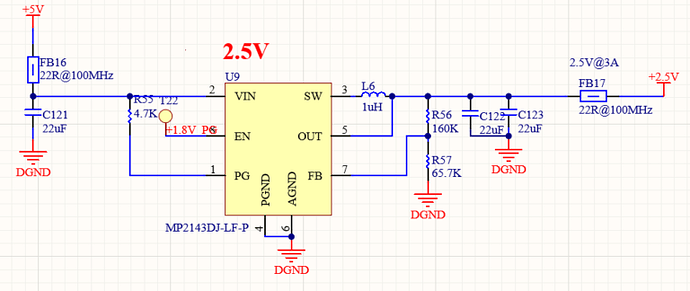

您好,我使用MP2143DJ-LE-P设计了5V输入,2.43V输出,具体电路图如下图所示,上电之后测得FB17端电压约为2.8V,VFB约为0.7V,VPG约为0.26V,我想问一下这是为什么呢?

1 个赞

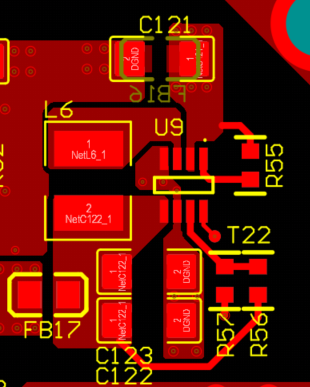

抱歉,R57实际焊接为52.3K,并非图上的65.7K,PCB layout如下图所示。

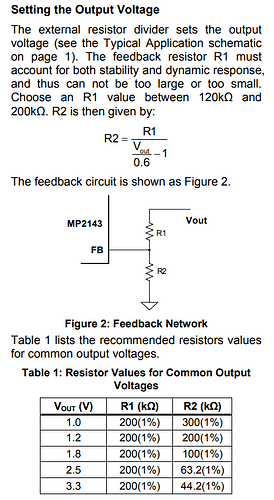

下图是手册P11关于PG的描述,实际测得FB pin voltage≈0.7V>0.6V(0.6V±10%),这里VFB是否受控呢?

您好,Layout看起来是可以工作的,其他层有完整的GND吗?VIN和EN引脚的电压是否稳定?您用的电感的饱和电流是什么规格,测试的时候有带负载吗?

其他层有完整的GND,VIN和EN电压是稳定的,我用到了多个MP2143,VIN和EN供电是相同的,只有这个输出异常,饱和电感用的是MPL-AY3020-1R0,模块为FPGA BANK供电,测试FPGA处于静态。

您好,是一块板子用到了多个MP2143这一个有问题,还是几个板子同一个位置的2143只有这个板有问题?有尝试更换过芯片吗?

一块板子用到了多个MP2143,更换过该位置的MP2143,更换后仍存在同样的问题

您好,可以尝试断开前后级的磁珠,给这一部分单独供电,再测试一下工作是否正常

1 个赞

好的,谢谢您

测试时VFB=0.7V,VPG=0.26V,其余MP2143的VFB=0.6V,VPG=VIN,这里的VFB受什么影响呢?

您好,需要看SW波形才能判断工作状态,FB电压只是外部电压分压过来的,但是PG被拉低说明芯片是知道输出电压异常的。有另外的板子可供测试对比吗?可以考虑FB下分压电阻是否接地良好

1 个赞

我断开FB17之后,模块空载,输出电压正常,焊接FB17,电压供给FPGA之后就恒定为+2.8V了,把R56和R57更换为其他比例电阻,输出仍未+2.8V

您好,可以测一下SW和VOUT的波形来判断工作状态

2 个赞