点击下图 ![]() 或下方链接可跳转至视频

或下方链接可跳转至视频

视频文字部分 ![]()

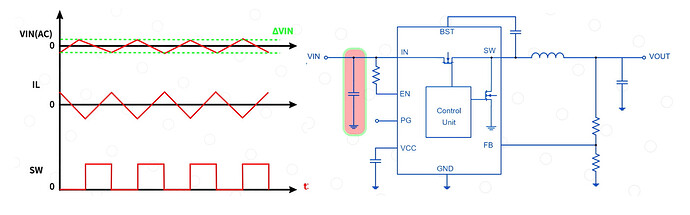

经常会被很多工程师朋友问到,Buck电源芯片在layout过程中,输入电容应当如何放置以及放置不好对芯片工作有何影响?今天我们就来谈一谈Buck电路输入电容位置放置的问题。

众所周知,Buck变换器在使用过程中,欲使输入端以最小的纹波代价,快速提供Buck变换器每个开关周期所需要的能量,输入端的MLCC是必不可少的;

图1:Buck变换器开关周期图

那么在实际layout的过程中,输入端的MLCC摆放到底有什么讲究呢?

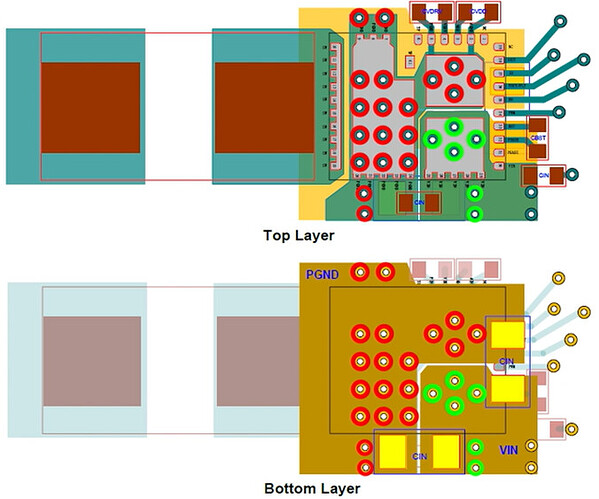

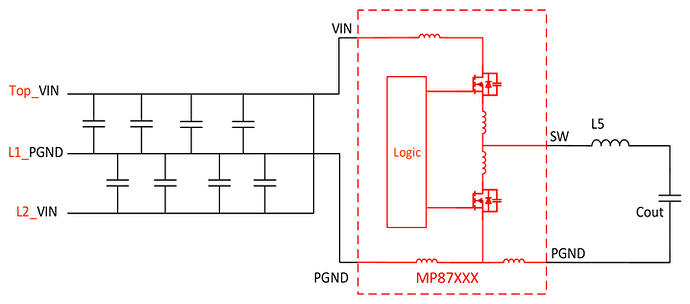

带着这个疑问,我们查阅MPS的大电流Buck变换器 MP87XXX的 Layout Guidelines一探究竟:

MP87XXX PCB Layout Guidelines:

1. Place the MLCC input capacitors as close to VIN and PGND as possible.

输入MLCC尽可能的靠近芯片VIN和PGND pin脚放置;2. Place as many VIN and PGND vias underneath the package as possible. Place these vias between the VIN or PGND long pads.

在芯片下方尽可能的多放置Vin和PGND的通孔,且通孔需要放置在芯片的VIN或者PGND的pad上;3. Place a VIN copper plane mid-layer 2 to form the PCB stack (positive/negative/positive) to reduce parasitic impedance from the MLCC input capacitor to the MP87000.

在PCB的L2层铺VIN的铜皮网络,使得Top层,L1层和L2层形成正/负/正的堆叠 结构,其目的是减小输入MLCC到MP87000的寄生阻抗。

Layout guidelines提到的这3点,究竟是从什么方面去考量的呢?下面我们对其进行逐条分析:

1. Place the MLCC input capacitors as close to VIN and PGND as possible.

输入MLCC尽可能的靠近芯片VIN和PGND pin脚放置;

图2:顶视图和底视图

我们简化输入MLCC到芯片VIN和PGND pin脚的Layout模型如下:

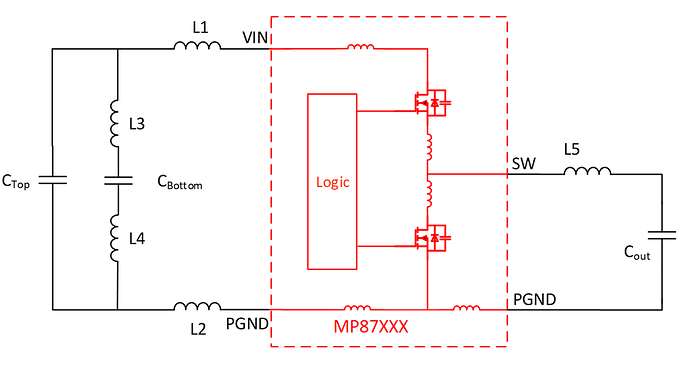

图3:简化后的芯片Layout模型图

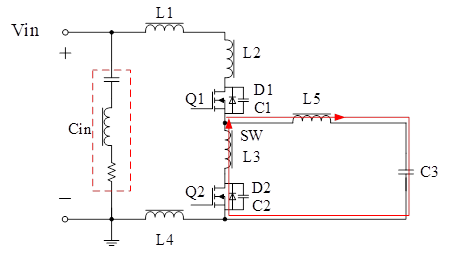

其中Ctop为top面的输入MLCC,Cbottom为Bottom面的输入MLCC,L1和L2分别为Top面输入MLCC到芯片VIN和PGND的寄生电感,L3和L4分别为Bottom面输入MLCC的VIN和PGND过孔的寄生电感,通过简化模型可以看出,输入MLCC靠近芯片VIN和PGND pin脚放置可以减小寄生电感L1和L2;

2. Place as many VIN and PGND vias underneath the package as possible. Place these vias between the VIN or PGND long pads.

在芯片下方尽可能的多放置VIN和PGND的通孔,且通孔需要放置在芯片的VIN或者PGND的Pad上;

图4:MLCC到芯片VIN和PGND Pin脚的寄生电感

对于Top面的MLCC来说,打VIN和PGND的通孔,除了连接内层VIN和PGND的铜皮以外,本质上是增加了VIN和PGND的电流路径,除了增加通流能力以外,还会使得不同层间的寄生电感并联,达到减小输入MLCC到芯片VIN和PGND寄生电感的目的。

对于Bottom面的MLCC来说,多打VIN和PGND的通孔,除了使得Bottom面的MLCC有更好的滤波效果以外,同时也会使得通孔间的等效电感并联,达到减小寄生电感L3和L4的目的。

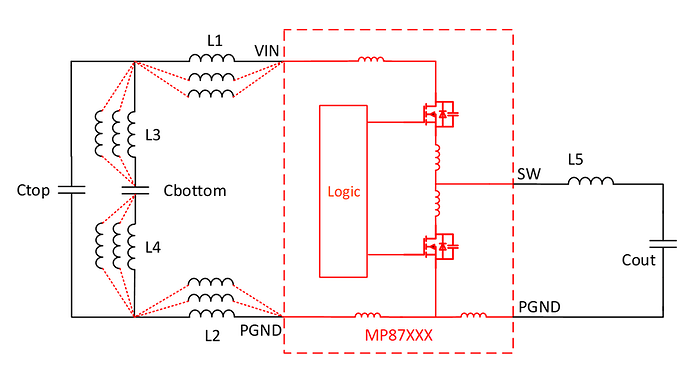

3. Place a VIN copper plane mid-layer 2 to form the PCB stack (positive/negative/positive) to reduce parasitic impedance from the MLCC input capacitor to the MP87000.

在PCB的L2层铺VIN的铜皮网络,使得Top层,L1层和L2层形成正/负/正的堆叠结构,其目的是减小输入MLCC到MP87XXX 的寄生阻抗;

MP87000 has not been released on MPS website yet. This part number is also mentioned in the video at 0:00:53.

图5:Top层、L1层和L2层形成正/负/正的堆叠结构

我们都知道PCB的层与层之间相当于一个寄生电容,那么当在TOP层,L1和L2层铺成正/负/正的网络时,由于通孔的存在,相当于在芯片的VIN和PGND之间增加了很多寄生电容,等效增大了输入MLCC的容值。

另外增加VIN或者PGND层数,本身就会减小输入MLCC到芯片间的寄生电感,第二条有提到,就不 再赘述;

综上所述,对于Buck变换器来说,输入MLCC的放置,一定要朝着减小输入MLCC到芯片VIN和PGND pin脚寄生电感的方向去优化。

那么为何要减小这两个寄生电感呢?下面我将从Buck变换器上下管电压应力的角度去分析原因;关于寄生电感对EMI的影响可以参考MPS电源小课堂之《汽车DCDC EMI》,这里就不再赘述。

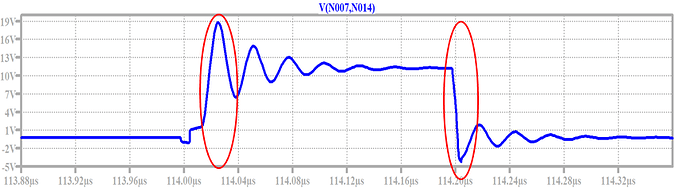

在Buck变换器下管电压应力测试中,当我们使用最小环测试芯片的SW 和PGND pin时仍然会看到如下类似波形,开关节点SW的上升沿和下降沿会产生很大的震荡,上升沿震荡的峰值远超过VIN电源电压,下降沿甚至会震荡到负值,过大的正压和负压都会造成下MOS管的损坏。

下面我们分别研究一下上升沿和下降沿尖峰产生原因。首先看一下上升沿尖峰产生的原因:

图6:上升沿和下降沿尖峰

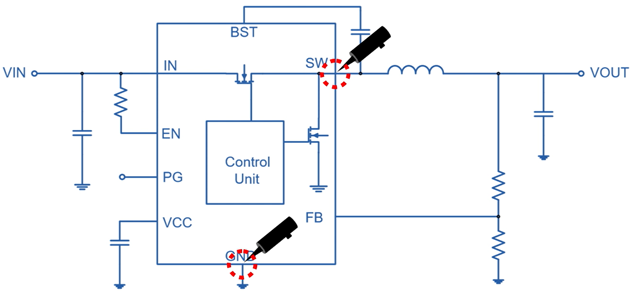

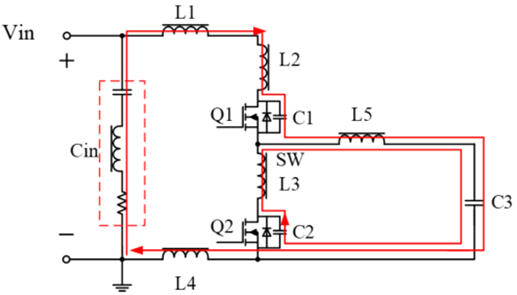

如下为Buck变换器等效模型:

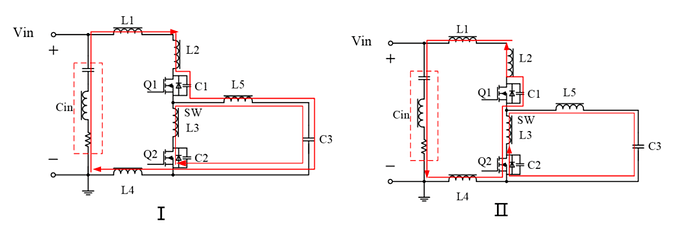

图7:Buck变换器等效模型

其中Cin为输入MLCC且包含寄生ESL和ESR;L1和L4分别为输入MLCC到芯片VIN和PGND的寄生电感;L2与L3为Buck芯片内部上下管MOS的等效寄生和引线电感,对于集成MOS的Buck变换器来说,L2和L3由芯片工艺和内部走线决定;L5和C3分别为Buck变换器的输出电感和输出电容;本文对Cin电容的ESL,ESR和L2,L3不做过多分析,重点讨论L1和L4的大小对Buck变换器上下管电压应力的影响。

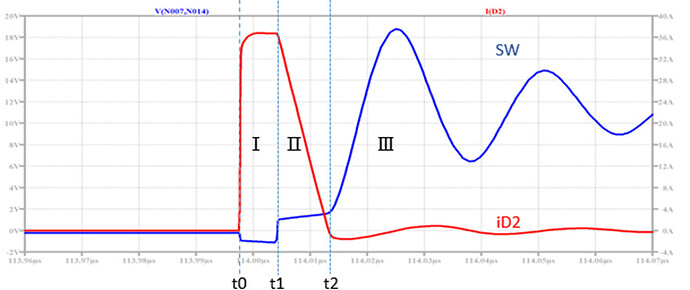

下面我们通过仿真波形来辅助分析SW上升沿震荡产生的原因:

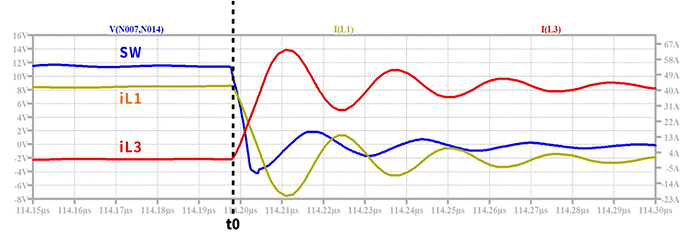

图8:仿真波形图

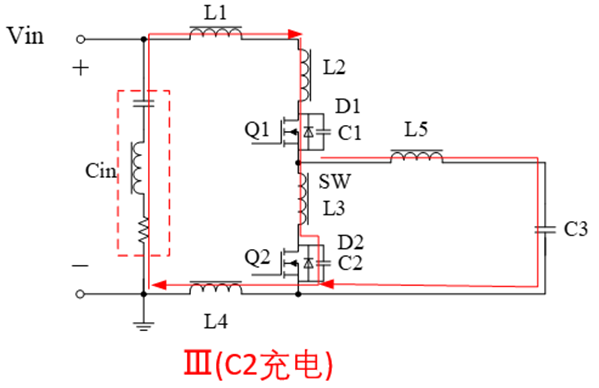

截取SW电压和下管体二极管iD2的波形,我们将波形分为Ⅲ部分:

Ⅰ:t0-t1时刻,Q1和Q2都关断,此时电感L5的电流由二极管D2续流,可以看到SW有-0.7V左右的二极管压降;

图9:t0-t1时刻Ⅱ:t1-t2时刻,t1时刻,Q1开通,此时二极管D2会承受来自Vin的反压,导致二极管电流迅速减小,由于二极管本身存在反向恢复,所以会看到二极管电流会变负;在这个过程中,D2,L3支路的电流减小,因此会在电感L3上面感生出上正下负的电压,这就是t1-t2时刻,SW第一段阶跃的原因;此时二极管D2仍在导通,C2还未进行充电;

图10:t1-t2时刻Ⅲ:t2时刻之后,iD2的电流因为反向恢复变为负值,此刻进入第三阶段,谐振阶段;

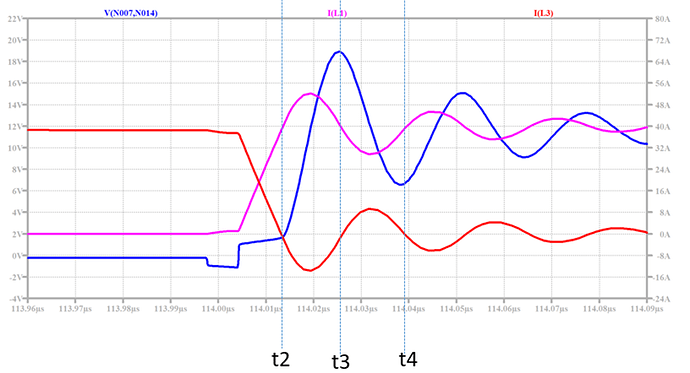

谐振阶段又可分为对C2充电和对C2放电二个阶段,仿真波形中增加电感L1和L3的电流iL1和iL3。

通过仿真波形可以看到:

图11:谐振阶段波形图

t2-t3时刻,电感电流iL1同时对C2和L5充电,此时SW点电压慢慢爬升,由于SW点电压小于Vin电压,iL1电流不断增大,因为负载电流恒定,因此电感L3电流不断增大,直到SW电压等于Vin电压时,电感L1电流达到最大,C2继续被充电,SW电压高于Vin,之后电感L1电流开始减小,iL3也开始减小,直到为0,此时C2停止充电,SW电压到达最高点,且iL1等于负载电流;

图12:t2-t3时刻

了解SW上升沿尖峰产生的原因之后,我们看一下L1和L4的大小对SW上升沿尖峰有什么影响呢?

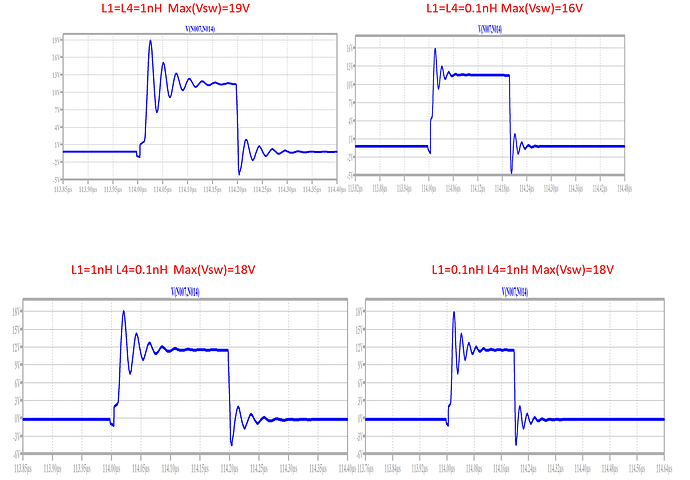

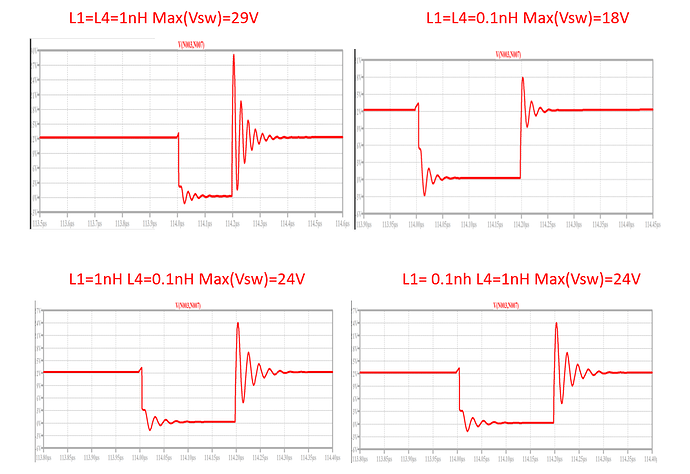

由于这两个寄生的电感的大小在实际的PCB中很难去精准量化,所以我们通过仿真的方式进行验证。仿真参数如下,通过选取4组不同的L1和L4的电感值,读取max(Vsw)值,结果如下:

图14:仿真结果图

通过仿真可以看到,L1与L4任何一个电感的感量大小都对下管SW上升沿尖峰的Max值都有影响,且L1与L4的感值越大,下管的SW的正向尖峰越大;

仿真参数如下:Vin=12V,Vo=0.8V,Io=40A,Fs=500K; L2=L3=500pH;C1=C2=5nF;Cin=40u,忽略寄生ESR,ESL;

下面我们介绍一下SW下降沿负尖峰产生的原因和影响因素。同样结合SW电压,iL1和iL3的电流仿真波形,可以看到:

图15:SW电压,iL1和iL3的电流仿真波形图

t0时刻,Q1关断时,Q2未开通时,输出电感L5电流可以近似认为不变,此时有两条电流支路为电感L5提供能量,分别为:

Loop1:L1-C1-L5-C3-L4-Cin-L1

Loop2:C2-L3-L5-C3-C2

其中Loop1的电流在减小,Loop2的电流在增加;对于电感L3来说,电感电流突然增加,就会感生出下正上负的电压,因此在SW的下降沿会看到负压;

图16:t0时刻电流流向图

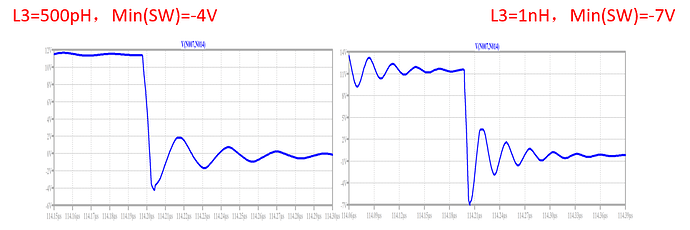

通过仿真,L3分别选择不同的感值,仿真结果如下:

图17:L3分别选择不同的感值仿真结果图

通过仿真结果可知负压的大小跟寄生电感L3相关,且感值越大,负压越负。

同样我们用最小环测试Buck电路上管电压应力时,也会经常看到在上管关断时,VIN-SW出现很大的电压尖峰,这个尖峰过大,同样会损坏上管。下面我们看一下这个震荡尖峰产生的原因;

图18: VIN-SW电压尖峰

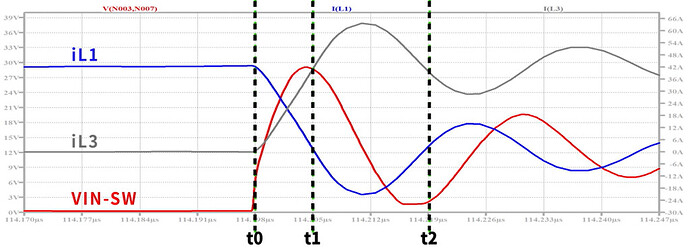

结合VIN-SW电压和电感L1和L3的电流iL1和iL3的仿真波形,根据iL1的过0点,把整个过程可以分为Ⅱ个段:

Ⅰ(t0-t1):t0时刻,Q1关断,电感L1上的能量经过L1-C1-L5-C3-L4-Cin-L1对C1进行充电。 iL1电流不断减小,在iL1电流过0时,C1停止充电,此VIN-SW电压到达最高点,此时进入阶段Ⅱ;

Ⅱ(t1-t2):t1时刻,当iL1过0时,由于C1电压大于Vin,因此C1经过C1-L1-Cin-L4-Q2-L3-C1进行放电,直到iL1电流为0,C1停止放电,VIN-SW电压下降到最低点,然后重复Ⅰ和Ⅱ这两个过程,由于线路寄生电阻的存在,最终VIN-SW电压稳定在VIN;

在整个过程中电感L5上的能量经过L5-C3-Q2 -L3-L5续流;

图19:VIN-SW、iL1和iL3仿真波形图及各阶段电流流向图

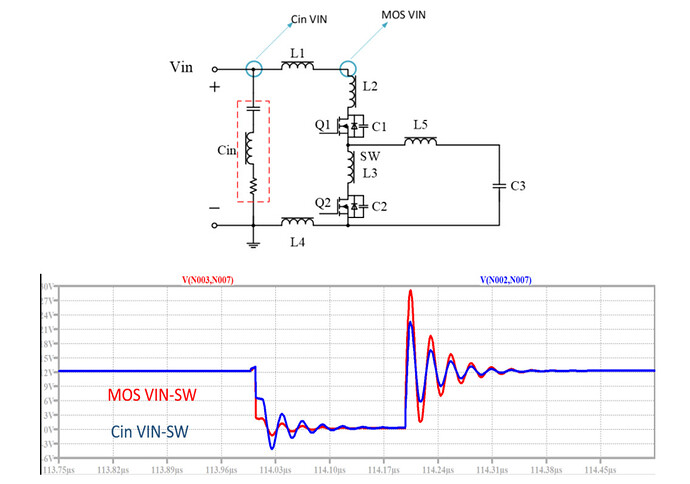

下面同样用仿真的方式看一下L1和L4的感值对Vin-SW尖峰的影响,依旧选取四组不同的电感参数。仿真结果如下:

图20:不同感值下的仿真对比图

由仿真结果可见L1和L4的大小都会影响上管关断时的电压应力,且感值越大,应力也会越大。

下面给大家分享一下不同的电压应力测试点,对实际的测试结果造成的影响。

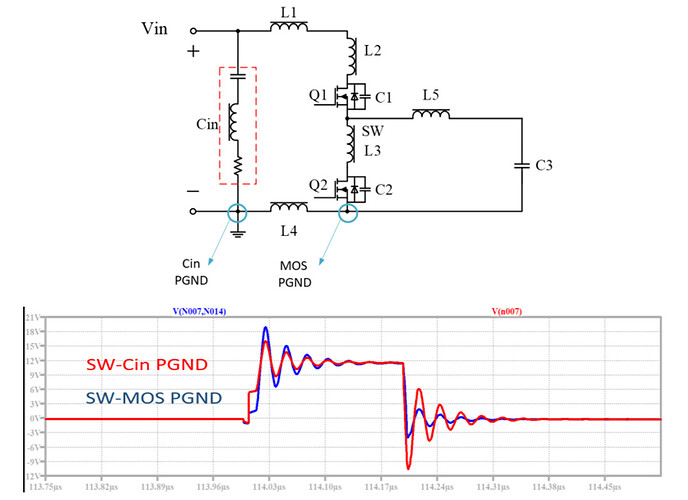

当我们在实际测试下管电压应力时,由于芯片pin脚不容易点到,很多时候探头的GND会放在Cin cap的GND上,此时测量会引入寄生电感L4的影响。通过仿真波形可以看到:以Cin cap的负极为GND,SW上升沿尖峰测试会偏小,SW下降沿尖峰会偏大。

图21:电压应力测试点在Cin cap的GND上

当我们在测试上管电压应力时,如果探头的正极放在Cin cap的Vin上,此时测量会引入寄生电感L1的影响;通过仿真波形可知:此时测出的电压应力会比实际值偏小;

图22:电压应力测试点在Cin cap的Vin上

如有相关需求可点击 MPS NOW 在线技术支持 , 工程师将为您直接提供项目技术支持服务

查看更多技术资源可访问:Resource Center

写的蛮好,有后续的整改的文章吗?

有视频讲解:https://www.monolithicpower.cn/cn/support/videos/mps-power-tips-2023-05.html

或者也可以关注我们微信公众号【MPS芯源系统】,搜索对应的标题,可以找到文章