良好的EMI是板级EMI设计和芯片EMI设计结合的结果。许多工程师对板级EMI的降噪接触较多,也比较了解,而对于芯片设计中的EMI优化方法比较陌生。今天,我们将以一个典型的Buck电路为例,首先基于EMI模型,分析其噪声源的频谱,并以此介绍,在芯片设计中,我们如何有针对性地优化EMI噪声。

一、Buck 变换器的传导 EMI 模型介绍

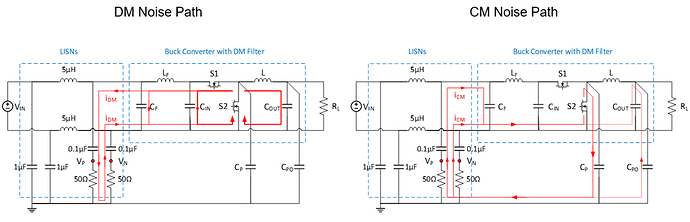

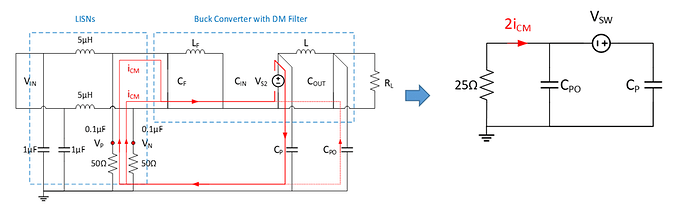

我们知道,电力电子系统中,半导体器件在其开关过程中会产生高dv/dt节点与高di/dt环路,这些是EMI产生的根本原因。而适合的EMI模型可以帮助我们分析噪声产生的原因。同时,由于传播路径的不同,EMI可以分为共模和差模噪声(可详见:汽车电子非隔离型变换器传导与辐射EMI的产生,传播与抑制)。图 1中展示了一个典型的Buck变换器差模和共模噪声的传播路径。

图 1中展示了一个典型的Buck变换器差模和共模噪声的传播路径。

图 1 Buck电路中差模和共模EMI的传播路径

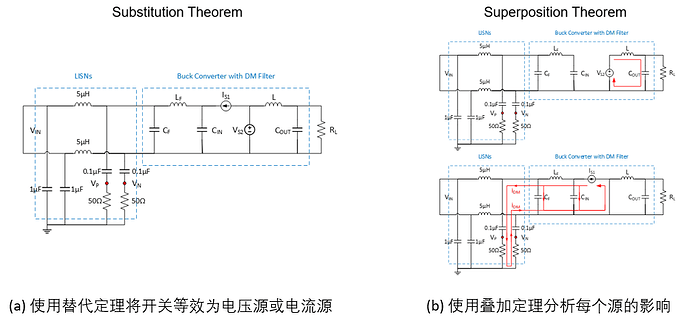

EMI建模的第一步是把开关用电流源或电压源进行等效,等效之后,电路各处的电流和电压依然不变。然后可以使用叠加定理来具体分析每一个源的影响。

以一个Buck 变换器为例,在图 2(a)中,我们将开关用电压源和电流源进行替代,由于差模电流不留经参考地,因此电路到参考地的寄生参数可以忽略。

在图 2(b)中,我们使用叠加定理对其分别进行分析,需要注意的是,当分析某一个源的影响时,其他的电压源需做短路处理,而其他的电流源需进行开路处理。由图 2(b)可知,实际上差模电流的源可以用Buck上管的电流等效,而最终的等效模型可简化为图 3的形式。

图 2 Buck 差模EMI噪声模型推导

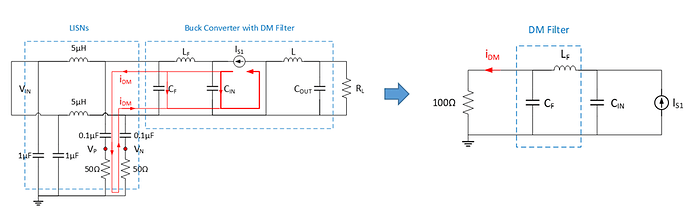

图 3 Buck 差模EMI噪声模型

由于差模噪声是由开关电源本身运行状态决定的,因此,降低差模噪声的主要方法是设计合理的差模滤波器,而与芯片设计关系不大。本次分享不会进行过多讨论。

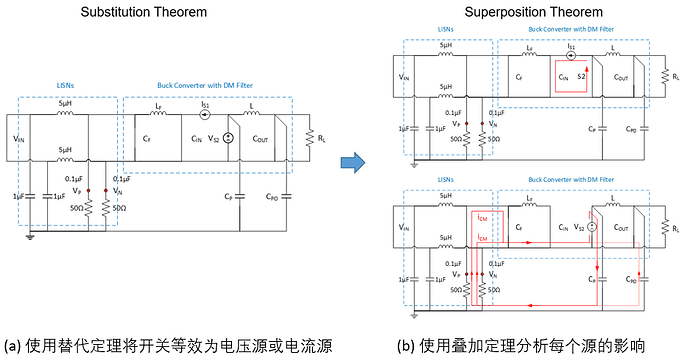

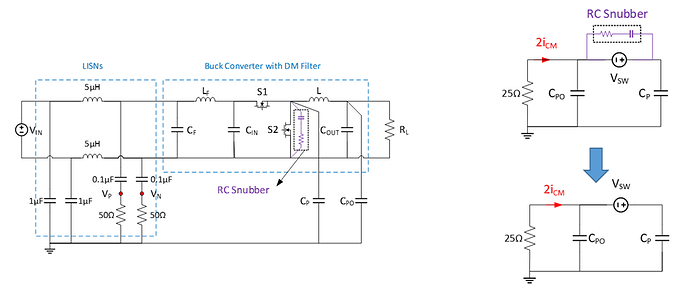

另一方面,对于共模EMI噪声来说,我们可以通过类似的方式进行建模,图 4展示了建模的过程。值得一提的是,对于共模噪声,由于输入、输出电容的阻抗通常远小于电路对地寄生电容的阻抗,因此在建模中,输入、输出电容可以作为短路处理。而最终的等效模型可简化为图 5的形式。

图 4 Buck 共模EMI噪声模型推导

图 5 Buck 共模EMI噪声模型

有点工程师朋友可能会有疑惑,这个模型如此简洁,那么一些其他的电路元件是不是被忽略了呢(比如图6 中所示的RC Snubber元件)?但实际上,答案是并不会。尽管EMI模型是相同的,但实际上开关波形会受到外部电路的影响,而这一部分已经被包含在了噪声源VSW中。而在电路分析中,与一个电压源并联的器件可以忽略。正因如此,我们可以看到,图6 中的RC snubber可以从最终模型中去掉。

图 6 对于并联元件的讨论

二、 EMI 共模噪声源的频谱分析

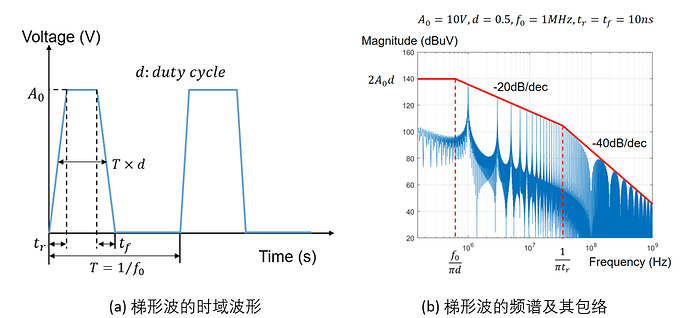

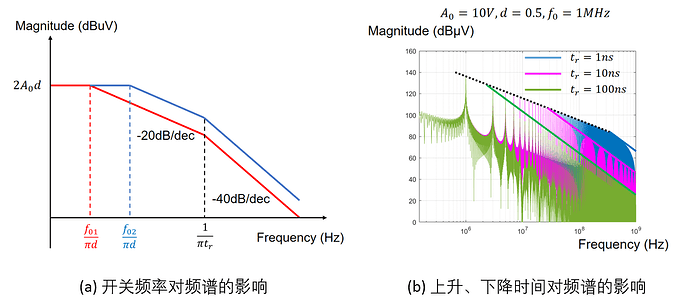

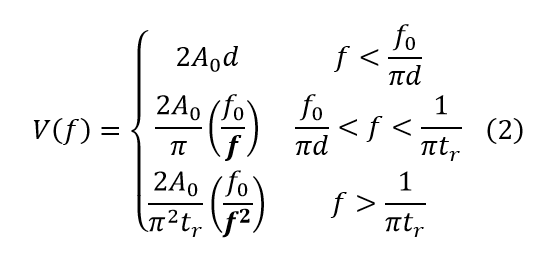

根据上一节的内容,我们知道对于Buck变换器来说,它的共模EMI噪声源即为开关节点的电压。在忽略开关振荡时,Buck开关节点电压波形可以等效为一个梯形波,如图7(a)所示。其中梯形波的幅值A_0即为Buck的输入电压,t_r和t_f对应节点电压的上升和下降时间,波形的周期T为Buck的开关频率f_0的倒数,d为buck电路的占空比。

图7

如果在频域上对这个波形进行分析,我们将会得到形如图7(b) 中的频谱,而它的包络线分为两段:从f_0⁄πd到1⁄(πt_r ) (t_r取上升时间和下降时间中的较小值),频谱的包络以每十倍频率20dB下降;而在1⁄(πt_r )之后,频谱的包络以每十倍频率40dB下降。

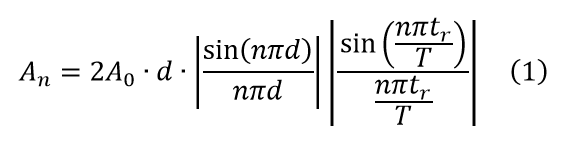

那这个结论是怎么产生的呢?实际上,如果对此梯形波进行傅里叶分解,我们将会得到如下的表达式,其中,A_n为其n次谐波的幅值。

对sin(x)/x这样的形式,在x<1时,sin(x)/x<1;在x>1时,sin(x)/x<( 1 )/x。因此我们可以将其简化为(2)中所示的形式,并依此画出包络线。对于f_0⁄πd到1⁄(πt_r )区间的表达式,函数与频率成反比;而在1⁄(πt_r )之后,函数与频率的平方成反比。因此我们得到了图7中展示的斜率。

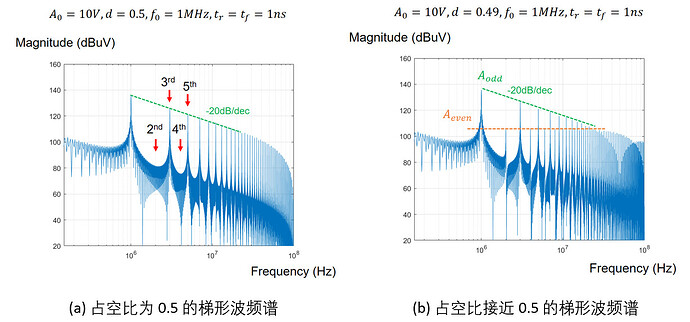

从(1)中我们还可以得到一些有趣的结论。如图8 (a)所示,如果d = 0.5,当n为偶数时,A_n=0,因此在频谱上是没有偶数次谐波分量的。另外,如图8 (b)所示,当d与0.5接近的时候,偶次谐波的包络约等于2A_0 |d-0.5|。对于汽车电子来说,12V转5V是一个很常见的应用,此时的占空比也比较接近0.5,可以用这个结论帮助进行分析。

图 8

从(2)中,我们也可以对开关频率以及上升下降时间的影响进行量化分析。在其他条件不变的前提下,如图9 (a)所示,如果开关频率提高十倍,高频EMI的噪声源会整体提高20dB;而如图9 (b)所示,如果开关上升/下降时间变为初始值的十分之一,则高频EMI的噪声源也会整体提高20dB。因此,提高开关频率虽然有助于减小电感元件,但确实也对EMI提出了更高的挑战。而对于芯片设计来说,MPS的大部分汽车电子芯片都支持客户通过模拟或者数字的形式来设置开关频率,从而帮助客户通过EMI测试。

图 9

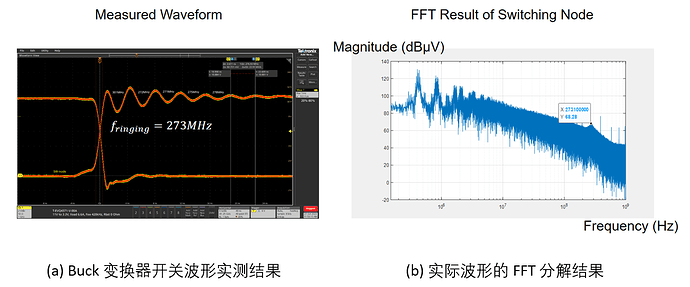

以上分析主要是基于理想开关波形,而实际开关波形(如图10(a)所示)则往往会带有一些振荡,而在EMI频谱上,在对应振荡频率的位置也会出现一个凸起(如图10(b)所示)。我们将在下一节中分析如何对这个问题进行优化。

图 10

三、 IC 设计中优化 EMI 的方法

A. 对开关波形振荡的优化

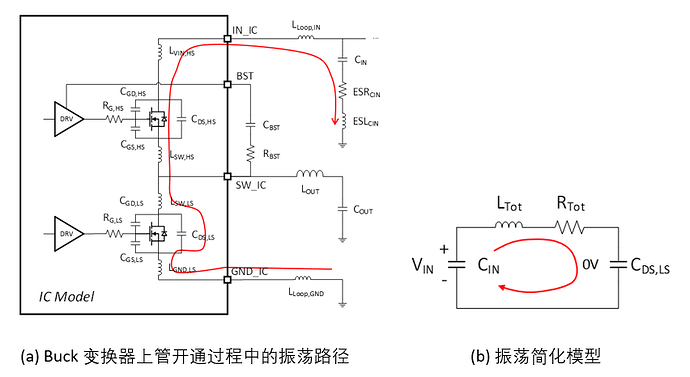

我们知道,在实际电路中,芯片、无源元件,以及PCB走线都会带来一些寄生参数。而在开关过程中,这些寄生参数会造成一些振荡。图 11(a) 中展示了Buck变换器上管开通过程中,形成开关节点振荡的回路,其中L_(Loop,IN), L_(Loop,GND)为PCB走线带来的寄生电感,L_(VIN,HS), L_(SW,HS), L_(SW,LS), L_(GND,LS)为引脚到芯片内部晶片各节点的引线电感,C_DS, C_GD, C_GS为MOS管的寄生电容。这个回路其实是距离芯片最近的一颗输入电容CIN与芯片上下管之间形成的回路。在谐振发生时,CIN上的电压较稳定,可以近似等效为输入电压VIN。

图 11

通过进一步简化,我们可以得到图 11(b)中的串联谐振模型,其中:

其中R_(FET,HS)为上管在开通过程中的电阻。值得一提的时,在开通过程中,FET处于饱和区,随着VG-S的增加,R_(FET,HS)会逐渐减小,最终达到导通电阻。

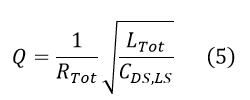

对于这个串联谐振,其品质因数Q如(5)所示:

我们知道,Q值越大,振荡越强烈。因此,为了从源头上减小这个振荡,我们需要做的是减小L_Tot的值,或者增大R_Tot和C_(DS,LS)。

在板级电路的设计上,是有一些方法来做到这点的。比如通过在下管并联一个RC snubber,可以等效增大电容;或者通过增加Bootstrap电阻来减小开通速度,从而等效增大谐振发生时的R_(FET,HS)。但这些方法也有一些副作用,如增加了损耗,也增加了电路成本。

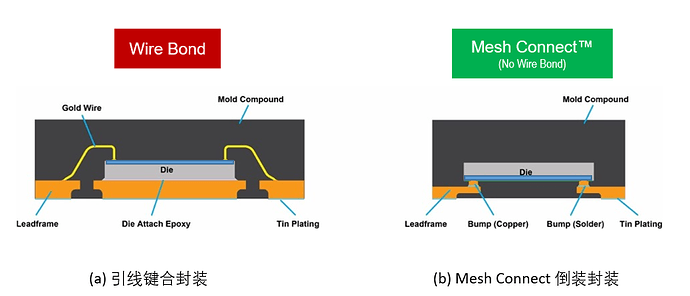

从芯片设计上进行优化的优势更明显,副作用更小。从封装技术上,相比传统的引线键合封装(如图 12(a)所示),MPS的倒装封装技术(如图 12(b)所示)大幅减小了封装带来的寄生电感,可将L_(VIN,HS), L_(SW,HS), L_(SW,LS), L_(GND,LS)等从nH级降为pH级。

图 12

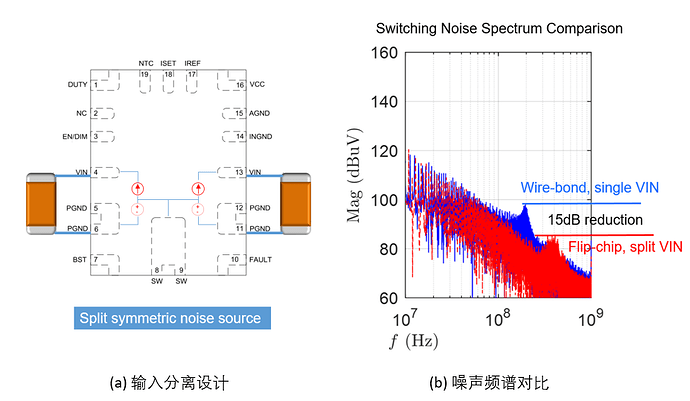

此外,由于振荡回路是由VIN与芯片内部上下管形成,通过将输入环路分离为对称的两部分(如图 13(a)所示),MPS可以进一步降低输入回路的寄生电感。图 13(b) 对比了引线键合、单输入封装和倒装封装、输入分离设计的两颗芯片的噪声源频谱。从图中可见,封装的改进带来了15dB以上的提升。

图 13

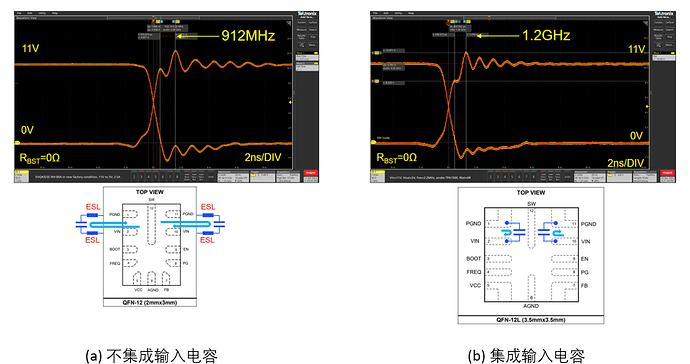

为了进一步减小输出回路的电感,MPS还可以进一步将输入电容也集成在封装之中。图 14 对比了集成输入电容的开关波形,由于回路电感进一步减小,谐振频率已经在1GHz以上,已经超过了许多EMI测试的要求范围。

图 14 开关波形与引脚示意图

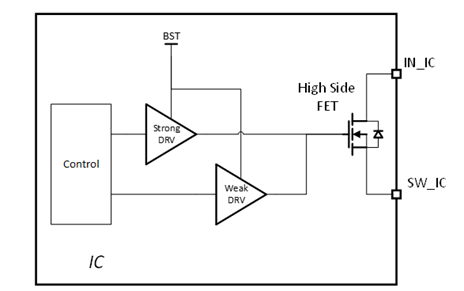

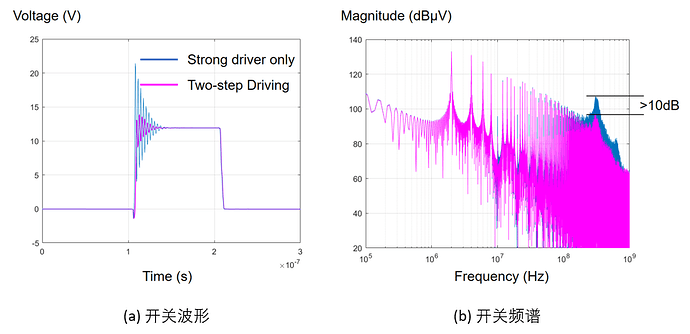

除了封装技术之外,在电路设计上也可以通过动态调整开关速度,使得谐振发生时,上管处于刚刚导通的状态,此时,R_(FET,HS)较大,从而可以有效抑制振荡强度。这一设计可通过设计多级驱动,并在合适的时间开通不同驱动来实现。图 15为一个两级驱动的示例。

图 15多级驱动(以两级驱动为例)

图 16比较了传统的单级驱动方式与两级驱动的效果。从图16(a)的时域波形上可以看出,两级驱动有效地降低了开关时的振荡,而从图16(b)的频谱上来,两级驱动也有非常明显的效果,将振荡产生的EMI峰值抑制了10dB以上。因为这一方法只改变了谐振回路中的电阻,因此谐振频率不会发生变化。

另外,值得一提的是,由于多级驱动实际上降低了开关速度,它对开关损耗是有一定影响的。但相比于增加Bootstrap电阻的方法,由于多级驱动可以动态调节开关速度,在谐振发生后,芯片可以加快管子开通速度,从而使得总开关时间仅有有限的增加,来减少过多的开关损耗。

图 16 单级驱动与两级驱动对比

B. 通过抖频设计优化EMI

抖频技术可以通过将开关能量分散到不同的频率上,从而有效降低EMI,这一部分在之前的分享中有详细介绍(可详见:选择合适参数进行抖频设计),因此在本文中暂略。

在本次的分享中,基于对噪声源频谱的分析,我们可以量化各个关键参数对于频谱的影响。另外,我们也介绍了芯片设计中降低EMI噪声的一些方法:从开关频率的选择上,MPS芯片支持多种开关频率的选择,部分芯片也可以开启抖频;从封装与布线设计上,MPS的倒装封装,对称输入设计,集成输入电容等技术可以有效降低高频噪声源;从驱动方法上,MPS独特的多级驱动可以有效减小开关振荡。

如有 相关需求/技术咨询/产品咨询 等可点击 MPS NOW 在线技术支持 , 工程师将为您直接提供项目技术支持服务

查看更多技术资源可访问:Resource Center