上一篇文章咱们讲了LDO输出电容容值的选型计算,今天咱们聊聊在选LDO输出电容时,输出电容的ESR,也就是等效串联电阻有哪些注意事项。别看它不起眼,这家伙可是LDO稳定性和性能的“幕后英雄”。选不好,LDO电路可能直接“罢工”,选对了,就能让你的设计稳如老狗!下面,咱们就深入了解ESR的要求和计算方法。

ESR是啥玩意儿?为啥这么重要?

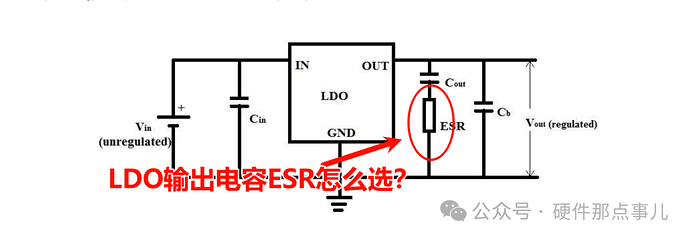

简单说,ESR就是输出电容上的一个等效串联电阻,它藏在电容内部,影响着LDO的动态响应和稳定性。LDO内部的控制环路需要电容和ESR默契配合,才能有一个稳定的输出电压。如果ESR太高,输出电压会不稳开抖;太低,电路可能直接“失控”,直接原地振荡开始跳舞。

ESR的作用在于引入一个零点(Zero),这玩意儿能抵消环路中的相位延迟,防止180°相移把系统搞垮。换句话说,ESR就是LDO稳定性的“调味剂”,得加得恰到好处!

如何选型计算输出电容的ESR?

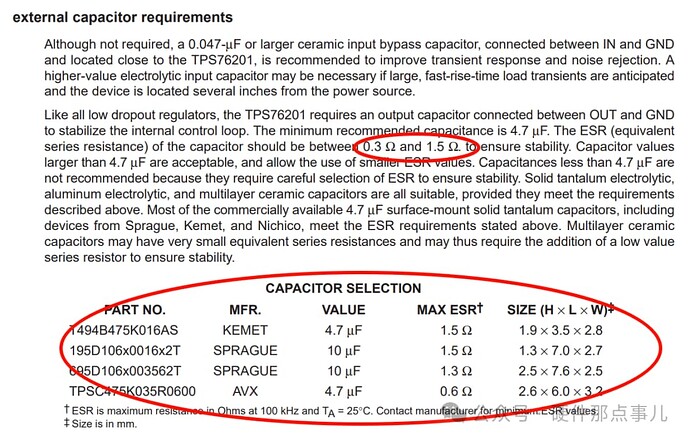

比如TPS76201的数据手册,它有说明ESR不是随便选的,它和输出电容容值有关系,而且有明确范围,数据手册推荐范围是0.3Ω到1.5Ω。

最小输出电容:4.7 µF(如果输出电容少于这个值,ESR得精挑细选,不然稳不住,如果电容超过 4.7 µF,ESR可以适当降低,但别贪心降到零。

为啥有这个范围呢?

因为LDO有控制环路,ESR太低,比如陶瓷电容的10-50mΩ,会导致补偿零点频率跑太高,压根赶不上极点节奏,容易导致振荡;ESR太高,比如老式铝电解电容在低温下飙升,电压跌落就跟坐过山车似的,稳不住输出。

再加上温度因素,低温下ESR可能会翻倍,尤其铝电解电容,所以选电容时得考虑“严冬考验”。TPS76201推荐的钽电容,比如KEMET的T494B475K016AS,ESR最大1.5 Ω,或陶瓷电容加小电阻,都是靠谱选择。

如何计算ESR?一步步来,别慌!

别以为ESR算起来像天书,实际上它很简单,就是根据LDO的稳定性需求和电容特性推导。

1.确定零点频率

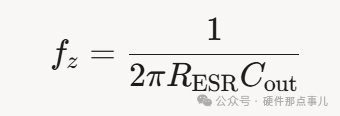

LDO 环路需要ESR引入的零点fz落在合适位置,通常在环路带宽内。公式是:

Cout:输出电容值。

RESR:目标ESR值。

fz:理想零点频率 (参考数据手册或仿真确定)。

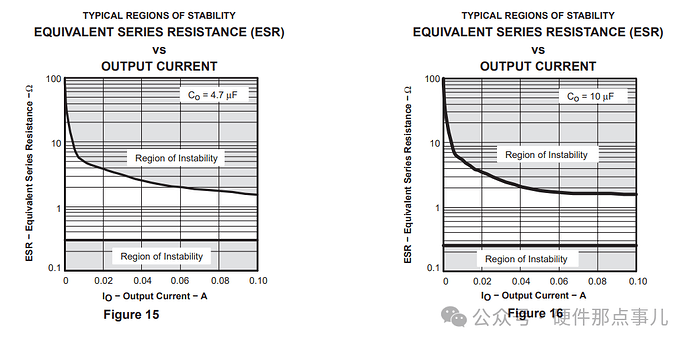

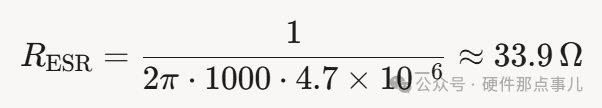

TPS76201 建议 Cout = 4.7 μF,如果想让 f约1kHz(—个常见环路带宽):

33.9Ω超出了1.5Ω范围!这说明直接用公式算得太粗糙,还是得参考数据手册的“安全区”。

当然我们也可以通过数据手册来反推ESR范围:

实际中,ESR范围是厂家根据环路仿真给出的“经验值”。TPS76201明确 0.3-1.5 Ω,意味着零点频率大约在22 kHz到106 kHz 之间(以 4.7µF 计算)。你得确保这个范围覆盖环路的极点频率,不然就得调整电容或加阻。

那如何选电容呢?

陶瓷电容:ESR太低(<0.1Ω),适合高频,但得加阻补救。推荐 X5R/X7R类型,4.7µF 起步。可以串联0.5Ω电阻,调到0.6-1Ω。

钽电容:ESR天然合适(0.6-1.5 Ω),可以直接上。TPS76201推荐的 KEMET T494B475K016AS(4.7 µF,ESR ≤ 1.5 Ω)是不错选择。

铝电解:容值大,但低温下ESR飙升,慎用。

布局来说电容离LDO输出引脚越近越好,减少寄生效应,不然ESR再好也白搭!

您好,非常感谢您得分享, 请教一下,LDO输出电容计算好都能满足LDO稳定要求,但是LDO提供电压给到后端的负载,需要并联大量的MLCC,对于LDO来讲,是不是ESR会进一步变小?会发生LDO的不稳定?应该如何解决呢?

确实会有这个问题,所以选LDO的时候注意一下,目前很多LDO内部集成了补偿机制,不依赖外部电容的ESR,你选的时候可以选这种的

但是这些古老的LDO还是有一定市场占有率的,不知道我提出的问题是怎么避免的?

你说的并联大量去耦电容是给后级IC去耦的吧?如果是去耦,那距离LDO输出端是比较远的,考虑线路阻抗,影响其实还好

这个“那距离LDO输出端是比较远的”,这个应该去量化。非常感谢。您有不依赖ESR的LDO推荐吗?非常感谢。

其实也能量化,就是计算起来需要花费精力去建立模型,你要想简单点可以仿真验证一下,LDO具体你可以去对应官网看看哈,型号我就不发了

非常感谢。

现代LDO也有可以使用陶瓷电容的型号,不一定要用钽电容了