现在各种设备都是朝着小体积高性能方向发展,那么如何减小DC-DC电路的占用面积呢?

一、影响DC-DC模块体积的因素

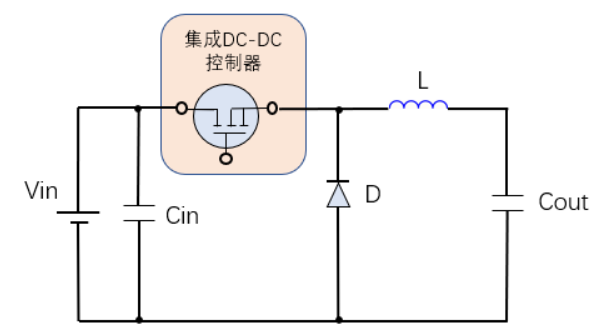

1. 常见DC-DC(BUCK)拓扑结构

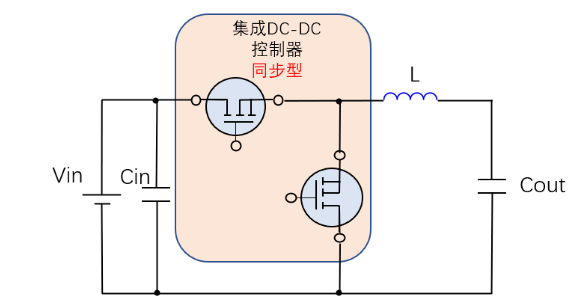

图1 BUCK电路拓扑结构

2. 外围器件分析

在如上图1所示的集成BUCK芯片的外围电路中,输入输出电容、二极管、电感均会影响整个DC-DC模块的体积。

二、如何减小电感体积

- 电感体积与什么参数有关

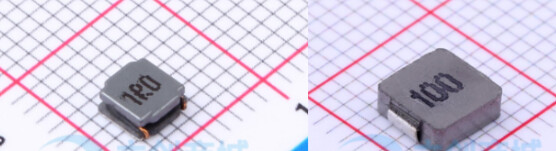

电感体积与其电感量有关,因为电感是通过绕线来增大感量,所以电感量越大,需要绕的圈数越大,即体积越大。参考下图2,10uH电感体积远大于1uH电感。

此外电感体积也和额定电流有关,额定电流越大,所需绕线的线径越粗,即体积越大。参考下图3,同样感量额定9A电感体积远大于额定4A的。

2. 如何降低电感量

前述可知减小电感体积只有降低电感电流与减小电感量两种方法,而电感电流与输出负载电流有关,这个我们没办法减小,因此只能去减小电感量。

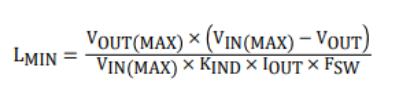

图4 电感计算公式

BUCK拓扑中电感最小值计算公式如上图4,其中Kind是指一个系数,表示电感器纹波电流与最大输出电流之比,此值一般在0.3左右,除此之外的VIN、VOUT、IOUT均为设计定下来的值,因此只剩下了Fsw可以用来调节电感的值,Fsw是芯片的开关频率。因此从公式可以看出,开关频率Fsw越大,所需电感量就越小。

以BUCK芯片为例,开关频率为1MHz,一般的典型应用推荐电感量为3.3uH,而典型应用中输入输出电压及输出电流一样的开关频率为285kHz的芯片,其推荐电感量大约15uH,不在一个数量级了

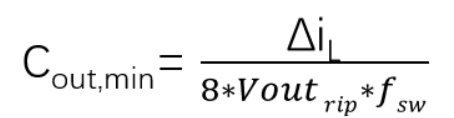

图7 输出电容计算公式

同时,如上图7的输出电容公式可以看出,输出电容容量也随开关频率的增大而减小,所以通过提高开关频率来减小体积是一举两得的方式。

但要知道的是,开关频率过高也不全是优点,过高的开关频率对EMC等可能有负面影响,同时高开关频率带来的损耗也更高

三、其他减小DC-DC模块体积的方法

1. 干掉二极管

选择如下图8所示的同步型BUCK芯片,由于同步型DC-DC不需要续流二极管,取而代之的是芯片内置的开关管,因此外围电路体积得以缩小。

- 从输入输出电容入手

为了滤除不同频段的杂波,通常输入输出电容都是并联多个,而在极端体积限制时,只要满足纹波等参数要求,可以减少输入输出电容数量;同理也可以通过减小其容值以缩小体积。

以上是站在开关电源角度,那么如果不用开关电源呢,我们都知道LDO外围电路非常简单,因此在散热及效率允许的条件下,优先使用LDO也是减小DCDC占用面积的好方法,那么同理,,也可以用电荷泵来减小面积

减少DC-DC变换器的面积或体积,以Buck变换器为例,可以通过以下方式完成:

1.提高开关频率。能减少储能器件包括输入电容、电感和输出电容的大小,这是最快速的方法,但是会增加开关损耗。

2.采用COT控制策略。在高瞬态响应要求的应用场景中,COT比传统电压电流模式具备更快的响应速度,因此在相同输出电压跌落大小的要求下,采用COT控制方式能实现更少的输出电容,进而减少电路面积。MPS有很多COT控制的芯片,在官网选择的时候,可以筛选控制模式为COT。

3.设计PCB磁元件。采用商用的电感往往无法实现最优的电感值、效率和体积的平衡,可以根据工程的参数要求设计一个PCB磁元件,这往往也能带来更薄的体积,可通过有限元仿真不断优化PCB磁元件的性能。

4.采用DrMOS。这能显著减小开关管的体积,尤其是一些半桥驱动芯片+2个NMOS的方案,能将其够变为单个DrMos实现。

5.采用MPS模块电源。除了通过理论的方式上减小变换器的面积,MPS作为芯片原厂,通过封装技术,能实现更优的功率密度减少体积。例如MPS的Intelli-Modules MPC22157-130等型号,能减少设计人员的工作量,缩短研发周期,并为系统提供稳定可靠的电源供应。