三、POE设计注意事项

由于POE规格较多,原理图设计请按照实际需要的规格,参考典型电路进行设计。本文重点讲解布板时的注意事项。

802.3af方案MP8017设计注意事项

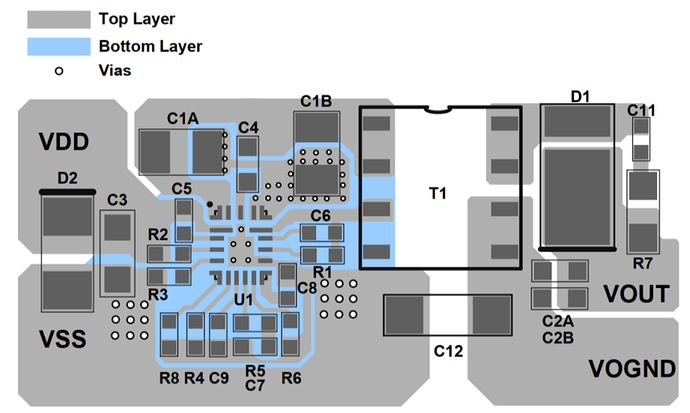

MP8017布板示例如下:

输入功率环路需要尽可能小,走线短而粗。输入功率环路为输入电容(C1B)→变压器原边(T1)→MP8017 SW脚(14脚)→MP8017 PGND脚(15,16脚)→回到输入电容的GND。功率走线需要尽可能粗,否则可能造成芯片带载能力不足。

输出功率环路需要尽可能小,走线短而粗。输出功率环路为变压器副边(T1)→整流二极管(D1)→输出电容(C2A,C2B)→回到变压器副边(T1)。 功率走线需要尽可能粗,否则可能造成芯片带载能力不足。

有源钳位功率环路需要尽可能小,走线短而粗。有源钳位功率环路为有源钳位电容(C4)→变压器原边(T1)→MP8017 SW脚(14脚)→MP8017 SNBR脚(17脚)→回到有源钳位电容(C4)。

VCC电容(C8)靠近芯片放置,最好和芯片放置在同一层,VCC电容的GND就近连接到芯片的AGND脚(11脚)。VCC电容的走线不要太细。

反馈电阻(R1)靠近芯片放置,走线不宜过长

热插拔器件(D2)、PD电容(C3)、VBUS电容(C1A)靠近芯片放置

DET,CLASS,COMP,VDIODE,SS,FSW等管脚的走线不宜过长

CP管脚的电容及BST管脚的电容靠近芯片放置,走线尽可能短

功率GND和信号GND采用单点连接的方式可提高芯片抗干扰能力

在MP8017底部放置过孔及足够的铺铜面积用以增强散热