一、POE协议握手简述

标准的POE在正式供电之前,会经过**检测(Detection),分类(Classification),启动(Start-up)**三个阶段。

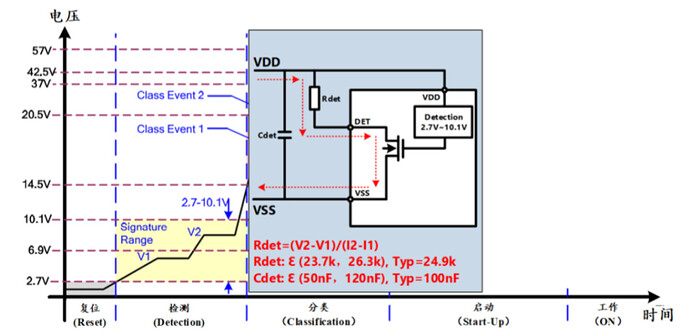

1. 检测(Detection)

连线的第一步是检测(Detection)阶段,是为了检测待供电的设备是否是标准的POE供电设备,这样可以保证48V电压不至于直接加在非PD设备上,保证设备的安全供电。

在检测阶段,PSE 会给出两组2.7~10.1V的电压,通过测到的电流去判断PD设备的特征电阻(Rdet)是否在协议的范围内,只有特征电阻在协议标准范围内,才会被判定为支持POE供电的设备,然后进入下一阶段。协议规定的特征阻抗在23.7k-26.3k之间,典型值24.9k。部分芯片集成了检测电阻(例如MP8030),而部分芯片需要外加(例如MP8017、MP8009)。

由于PSE是通过检测电流来检测特征阻抗,这也就意味着输入电容不能太大否则会影响电流检测。协议要求输入电容要在50nF-120nF之间,典型值100nF。

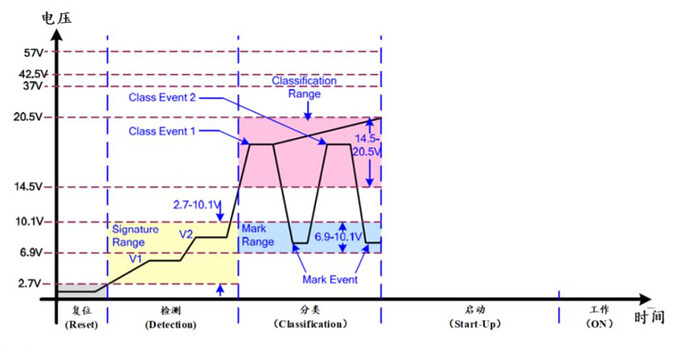

2. 分类(Classification)

此阶段主要是为了确定 PD 设备的功率等级,这一阶段的 PSE 会向 PD 端给出14.5~20.5V的电压,通过检测的电流对 PD 设备的功率等级进行分类。其中 class0~3 等级只会给一组电压检测功率等级,后面就开始启动过程;而 class 4 等级会给两次电压确定功率等级,然后才会开始启动后续的供电过程。bt协议则会进行更多轮的分类过程。

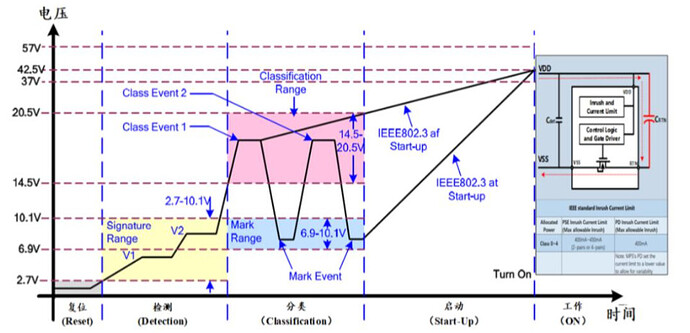

3. 启动 (Start-up)

启动阶段主要是给 VDD 和 RTN 之间的电容进行充电,因协议限制了此阶段的最大允许浪涌电流(Inrush current),所以会限制通过 RTN 到 VSS 之间 MOS(Pass Switch)的电流,达到软启的目的,直到VDD和RTN之间的电容充电到指定值,才会完全打开RTN到VSS的 Pass Switch 进行正常的 POE 供电。

完成这三个阶段,PSE即可给PD提供所需电压及功率。

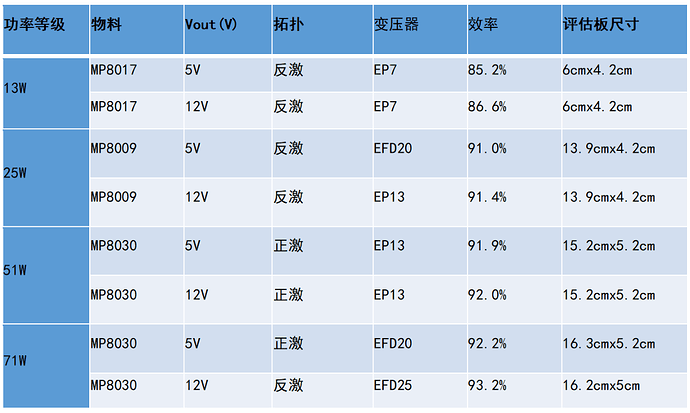

二、选型推荐

MPS选型推荐如下表。MPS可提供完整的PD设计资料,包含原理图、pcb、bom、变压器规格书、测试报告。

扫码进群获取MPS PD参考设计原文件:

三、POE设计注意事项

由于POE规格较多,原理图设计请按照实际需要的规格,参考典型电路进行设计。本文重点讲解布板时的注意事项。

802.3af方案MP8017设计注意事项

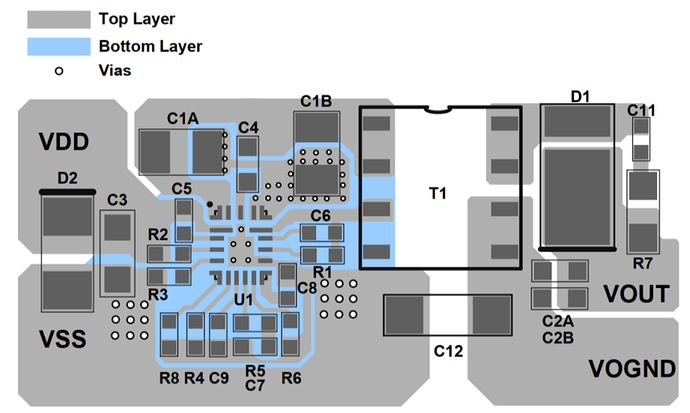

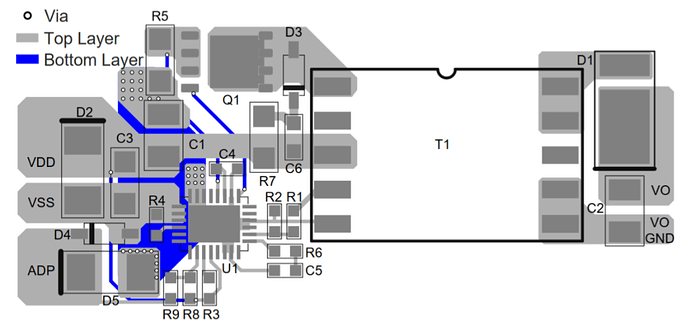

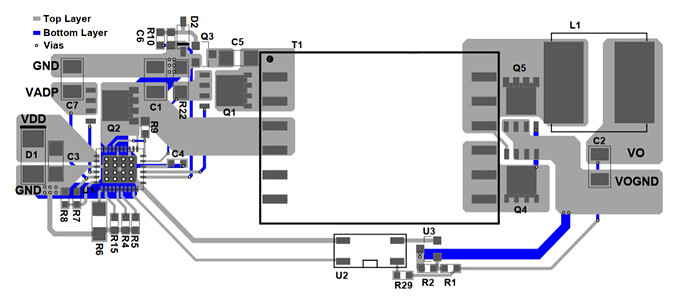

MP8017布板示例如下:

-

输入功率环路需要尽可能小,走线短而粗。输入功率环路为输入电容(C1B)→变压器原边(T1)→MP8017 SW脚(14脚)→MP8017 PGND脚(15,16脚)→回到输入电容的GND。功率走线需要尽可能粗,否则可能造成芯片带载能力不足。

-

输出功率环路需要尽可能小,走线短而粗。输出功率环路为变压器副边(T1)→整流二极管(D1)→输出电容(C2A,C2B)→回到变压器副边(T1)。 功率走线需要尽可能粗,否则可能造成芯片带载能力不足。

-

有源钳位功率环路需要尽可能小,走线短而粗。有源钳位功率环路为有源钳位电容(C4)→变压器原边(T1)→MP8017 SW脚(14脚)→MP8017 SNBR脚(17脚)→回到有源钳位电容(C4)。

-

VCC电容(C8)靠近芯片放置,最好和芯片放置在同一层,VCC电容的GND就近连接到芯片的AGND脚(11脚)。VCC电容的走线不要太细。

-

反馈电阻(R1)靠近芯片放置,走线不宜过长

-

热插拔器件(D2)、PD电容(C3)、VBUS电容(C1A)靠近芯片放置

-

DET,CLASS,COMP,VDIODE,SS,FSW等管脚的走线不宜过长

-

CP管脚的电容及BST管脚的电容靠近芯片放置,走线尽可能短

-

功率GND和信号GND采用单点连接的方式可提高芯片抗干扰能力

-

在MP8017底部放置过孔及足够的铺铜面积用以增强散热

四、POE常见问题解答

1. PD没有输出怎么办

PD包含两部分,一部分是POE协议控制部分,用于与PSE握手使得PSE产生48V(典型值)输出电压;另一部分是功率转换部分,将48V转换为需要的电压。

如果PD没有输出,先看VDD电压,VDD电压正常在37V~57V之间。如果VDD电压过低,那么是在协议握手阶段出现问题,需要重点检查协议握手相关器件是否参数配置正确。如果VDD电压正常,则是DCDC功率转换部分出现问题,需要检查DCDC功率转换部分,此时也可以断开PSE单独给PD供电48V来进行调试。

2. 协议规定PD的输入电容需要小于120nF,而DCDC功率转换又需要比较大的输入电容,如何解决这个冲突

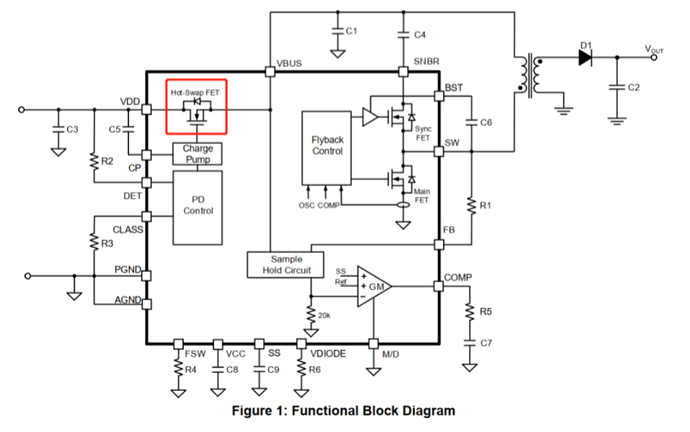

以MP8017为例,如下图。C3为协议检测的电容,C1为功率转换的输入电容。PD芯片内部一般都会有一个MOS用来隔断,在协议检测阶段,MOS不会开启,此时只有C3连接进电路中,C1不会干扰协议检测。而当VDD电压建立起来之后,MOS导通,C1才会工作起来。

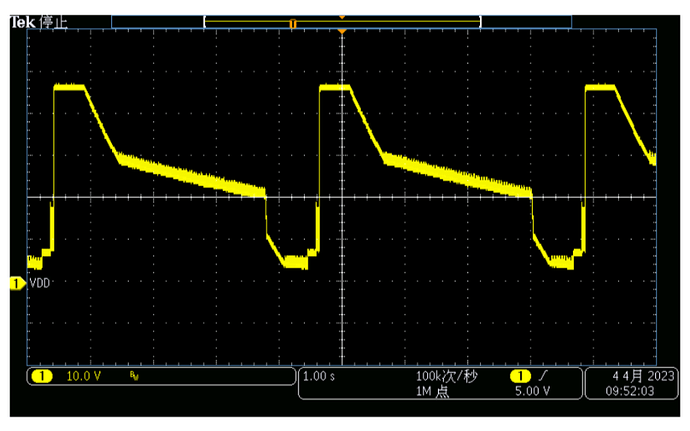

3. 输出电压在周期性地建立又跌落是怎么回事

这个现象发生在空载或者轻载下是正常的,带负载之后即可稳定。

为了保护不支持POE协议的设备,POE协议规定了维持PSE电压输出的最小功率要求。PD必须维持一定的功率,PSE才会认为PD设备正常连接着,PD功率过小,PSE则会认为PD设备已拔出,便会关闭48V输出。而关闭后PSE会周期性地发送握手信号以检测新设备是否插入,PD设备在连接好的情况下还是可以正常和PSE握手的。因此在PD轻载或者空载时,会出现输入电压及输出电压周期性地建立又跌落的情况

4. PD能否支持24V适配器输入

MP8017不支持24V适配器输入,可支持48V适配器输入。MP8009和MP8030支持24V/48V适配器输入,但是参考设计的变压器是按照37V~57V输入范围设计的,如果想要支持24V适配器输入,需要重新设计变压器。

5. PD是否支持24V输出

MP8017、MP8009、MP8030均支持24V输出,同样也是需要在参考设计的基础上重新设计变压器。

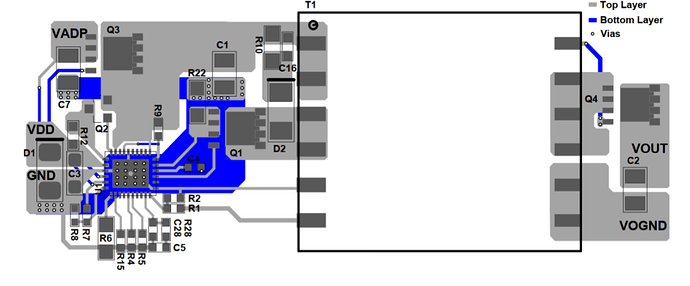

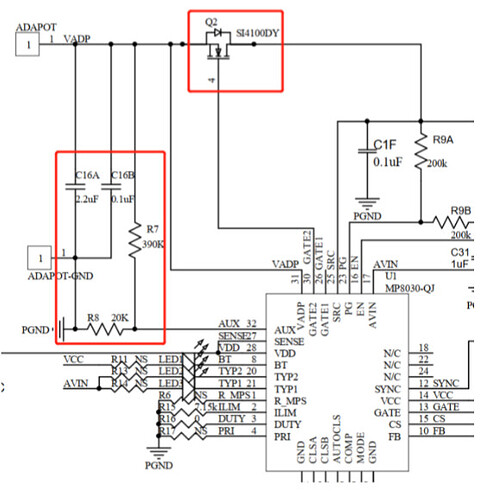

6. MP8030如果不需要适配器输入如何连接

将下图红框中的器件去掉,AUX、VADP接到PGND即可

7. 现有参考设计的效率不能满足要求,能否进一步提高效率呢

参考设计是效率和尺寸两相权衡之后的方案,如果要进一步提高效率,可以通过增加变压器线径、非同步整流改成同步整流、选用性能更好的MOS等方式,但是会使得整体尺寸变大

——————————————————————————————————————————

编著人:@ Baily Wen

1 个赞