802.3bt方案MP8030正激设计注意事项

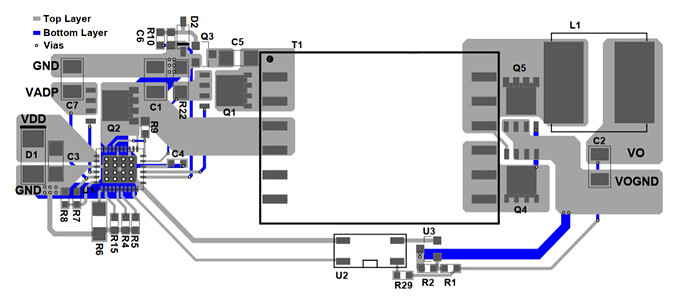

MP8030正激拓扑layout示例如下:

VCC电容必须靠近芯片放置,且VCC电容的GND需要以较短路径回到芯片GND。

SRC(25脚)为功率管脚,需要铺铜而不是走细线。

输入的功率环路为输入电容(C1)→变压器(T1)→原边MOS(Q1)→采样电阻(R22)→回到输入电容的GND。需要保证输入功率环路尽可能小,走线尽量粗。输入陶瓷电容尽量放在环路最里面,电解电容等靠近环路外面放(也就是陶瓷电容相比电解电容需要更靠近变压器)。

保持吸收电路的环路尽可能小。吸收电路的环路为输入电容(C1)→变压器(T1)→C5→Q3→回到输入电容GND。

输出有两个功率环路,也需要尽可能保证功率环路小,走线粗。第一个环路为变压器输出正端→输出侧电感(L1)→输出电容(C2)→功率MOS Q4→回到变压器输出负端。第二个环路为电感(L1)→输出电容(C2)→功率MOS Q5→回到电感(L1)。输出的陶瓷电容处理方法与输入电容一样,陶瓷电容放在环路最里,电解电容靠外。

COMP走线尽量远离变压器,功率MOS(Q1)等容易引起干扰的器件。

原边电流采样电阻R22连接到CS引脚的走线不宜过长,最好也避开容易引起干扰的器件