本测想要设计的是输入400Vdc,输出21V/5A,主要应用于100W PD应用。在100W USB-PD适配器这一典型应用中,LLC已经是基本的主流拓扑了,效率高、功率密度大是其主要的特点,EMI也会比较好控制,不过对于LLC的调试确实非常漫长的,在其谐振网络中包括Lr、Cr、Lm、Q、Ln等众多参数,这些参数都是相互耦合的,往往牵一发就要动全身。

这次使用MPS的LLC设计工具来代替这些繁琐的调试步骤,给出几个比较好的最优解。

首先要确定的就是输入输出的限值,其中输入时400V,实际上这是一个典型电压,需要给出一般的最大最小电压,PFC输出通常为380V~410V,预留一定裕量达到360V~420V,对于100W这种应用,设计谐振频率通常在100kHz左右,输出过载按照10%预留,电路规格要求如下图:

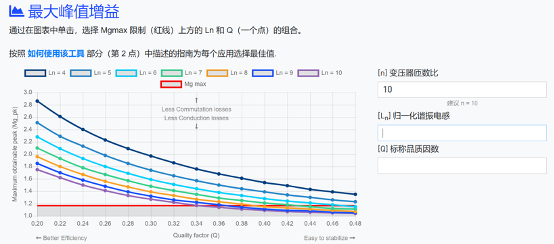

接下来进行峰值增益的计算,会给出几个最佳的组合:

变压器的最佳匝数是直接给出来的,建议按照建议的来;LLC 的设计本质就是确定谐振腔的三个核心参数Lr、Cr、Lm,而工具通过控制Q和Ln进行选择,当降低Ln 值时,最大峰值会增加,但Lm值也会相应降低。这将有助于实现ZVS条件,但也会在输入电流中引入更高的纹波,从而导致更高的传导损耗。Q值越大,带宽越窄,增益也越低。作为一般考虑,当我们增加Q值时,开关频率随之增加,会导致更大的增益变化。这对稳定响应来说并不利。所以Q越低系统越稳定。由上图可以看出来Ln的选择基本就是在4-5比较合适,也比较符合个人对于100W适配器应用的习惯,基本上都在红线以上,效率和稳定性都比较折中。对于Q的选择个人比较习惯选择0.45附近的.

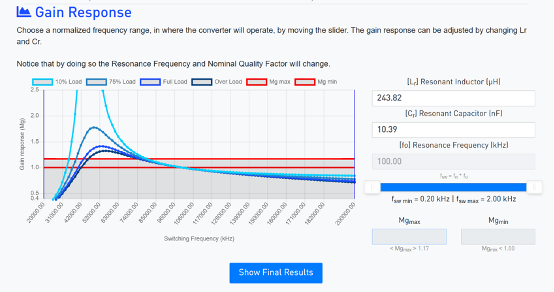

这个模块出现了问题,也不知道是浏览器的问题还是什么原因,图形中的Fsw与移动滑块选择的单位不一致,导致不管怎么选择图形中的滑块都不动,也就没法确定Mgmax和Mgmin

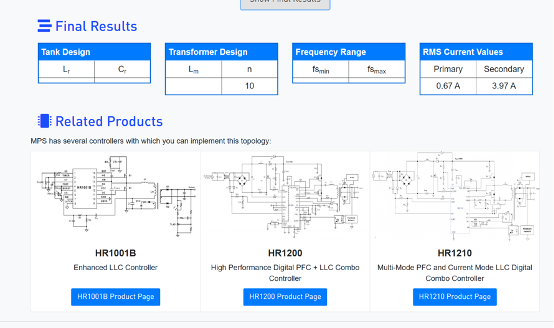

这也导致了在最终结果中看不到一些参数的结果:

不过对于这样的设计,还是给出了一些参考方案。