大家好,我是做汽车电子硬件十多年的老鸟,也搞过很多集成DCDC模块的EMC认证。最怕的就是3米法辐射和CISPR25传导测试,动不动就超标5~10dB,调试起来真是头大。

最近逛MPS论坛,发现yige.wang工程师在论坛上分享过一篇《汽车电子DCDC芯片的EMI优化设计》,干货很实在,今天咱们就借锅下饭,理论结合实际聊一聊如何做好DCDC芯片的EMI优化设计,这年头论坛该逛还是要逛,毕竟AI的回答有时候会有错觉,你可别将错就错,有问题提提问,硬件问题还是真人回答比较踏实。

先说清楚:DCDC开关噪声到底长什么样?

DCDC,尤其是Buck开关噪声从来不是单纯的开关频率fsw,而是“基波+一堆高频谐波”的混合体。

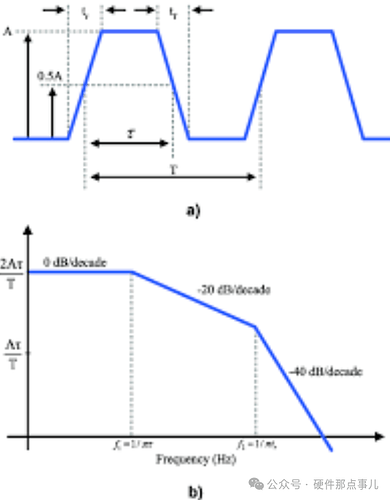

开关管电流近似三角波,开关节点电压近似梯形波。梯形波的谐波包络分成三段:

低频段(f < 1/πtr):幅度 ~ 1/f

中频段(1/πtr < f < 1/πtf):幅度 ~ 1/f²

高频段(f > 1/πtf):幅度 ~ 1/f³(tr、tf是上升/下降时间)

有兴趣的话可以用MATLAB算一个案例:Vin=12V,Iout=5A,fsw=2.2MHz,tr=tf=5ns vs 20ns。

你会发现tr=5ns时,100MHz处谐波比tr=20ns高整整15dB。

换句话说,开关越慢,高频分量衰减越猛。这就是为什么很多车规芯片故意把驱动电流拉软的原因。

再看频率本身:fsw越低、Duty越大,2f、3f等倍频处的能量也越分散。我算过Duty=0.5 vs Duty=0.8(fsw都固定2MHz),3f处的峰值能差4~6dB。所以选频率时别只看效率,得把倍频躲开车载收音机AM/FM频段(0.5~108MHz)和CISPR25重点考点。

那开关频率怎么选?

有人干啥都喜欢拍脑袋,结果EMC一测,那就是一拍一个不吱声,所以别拍脑袋,可以用下面这套公式:

开关损耗占比 ≈ 0.5 × Vin × Iout × (tr + tf) × fsw / Pout

滤波电感体积 ∝ 1/fsw

举个例子,原来用1MHz,L需要22μH,改成2.2MHz后L降到4.7μH,体积减半,但开关损耗从1.2W涨到2.1W。这个时候可以把tr拉到15ns,损耗又压回1.6W,同时100MHz以上高频噪声掉了12dB,完美折中。

抖频Spread Spectrum技术香不香?

MPS很多芯片都有FSS Frequency Spread Spectrum功能,调制深度一般±5%~±10%,三角波调制。怎么去量化评估这玩意的好处呢?

峰值降低量计算公式(CISPR25传导,RBW=9kHz):

ΔdB ≈ 10 × log₁₀(Δf_mod / RBW)

Δf_mod = 2.2MHz × 8% = 176kHz

ΔdB ≈ 10 × log₁₀(176k / 9k) ≈ 12.9dB

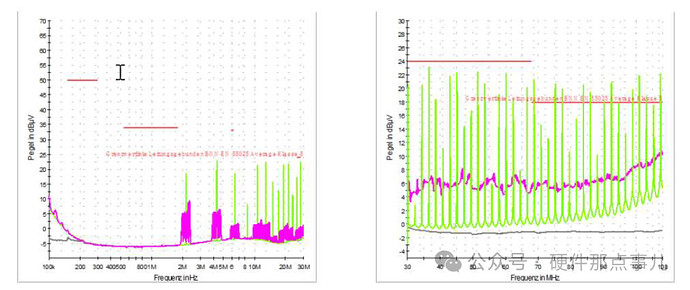

以MPQ4430(频率2.2MHz)为例,无FSS和开FSS后的传导测试结果对比:

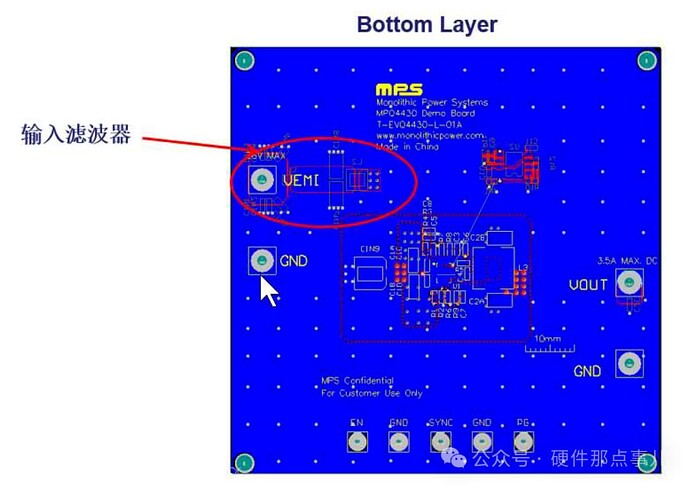

输入差模滤波器你千万可别忘了!

经典LC滤波器,两级时衰减≈40dB/dec。截止频率fc = 1/(2π√(L×C))

如果搞两级,那效果绝对杠杠的!当然也更贵,比如:

第一级:Ldm=2.2μH + Cdm=10μF陶瓷 → fc≈34kHz

第二级:再加0.47μH + 4.7μF

500kHz处衰减>35dB,1MHz处>45dB,轻松把传导压下去。当然记住电容一定要选低ESL的封装。

环路面积减一半,EMI掉6dB!

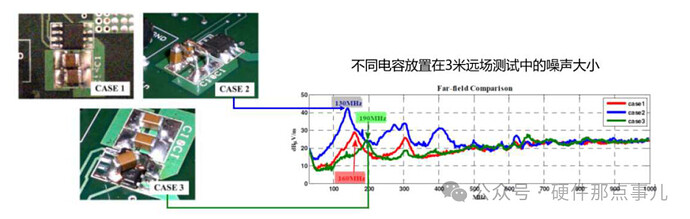

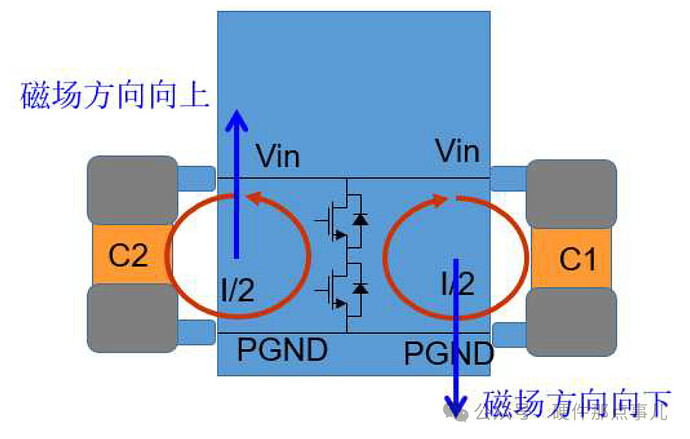

还有就是最核心的高频电流环路一定要注意,这玩意面积减一半,EMI可以掉6dB。

磁场强度B ∝ I × Area / r³

辐射电场E ∝ f² × Area × I

所以环路面积每缩小1/4,辐射理论上掉12dB,当然了这只是理想,实际会打点折扣,也能掉8~10dB。

对比三种方案同步Buck芯片,同步方案减少高频电流回路面积,同步buck集成MOSFET,高频电流环路更小,磁场强度更弱,所以EMI效果更好。

再把输入电容紧贴VIN-PGND Pin(距离<3mm),面积进一步压缩,3米法辐射结果,芯片内部集成输入电容,对EMI有巨大的帮助,可以极大的减小高频环路噪声,对传导和辐射都有很好的改善;

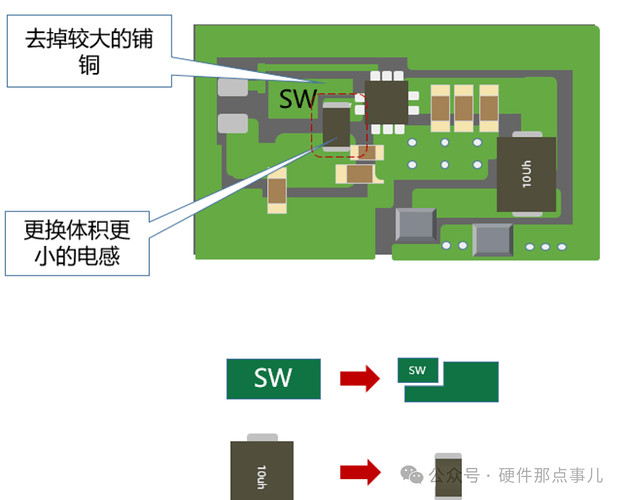

开关节点SW+电感要控制好!

SW节点到电感的走线越短越好。寄生电感Ls每多1nH,尖峰电压ΔV = Ls × di/dt(比如di/dt是5A/ns,那ΔV=5V!)。MPS的电源模块把电感直接封在芯片里面,SW走线几乎为零。所以这个就牵涉到以前咱们聊过的一个话题,就是SW节点铺铜是越大越好?还是越小越好呢?相信你现在肯定有答案了,如果没有,狠狠地补课去吧!

最后就是PCB布局了

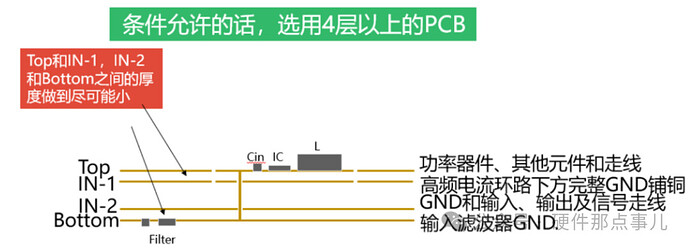

首先多层板肯定比单层板或者2层板EMC性能更好,4层板及以上(Top-Signal-GND-Bottom),对4层板来说,Top和IN-1,IN-2和Bottom之间的厚度为什么要做到尽可能小呢?

DCDC的高频电流,尤其是SW节点和输入电容之间的环流,在Top层走出去,回来必须走最近的GND平面。这个回路不是平面的,而是立体环路:

正向电流在Top,返回电流在内层GND,两者之间隔着介质厚度h

环路面积 = 走线长度 × h

面积越大 → 磁偶极子越强 → 辐射电场 E ∝ f² × Area × I

h每减小一半,辐射理论上直接掉6dB。

高频电流环路下方完整GND铺铜,返回电流几乎正下方走,环路面积最小化,当然EMI布局从来不是全板铺GND就赢,而是高频功率区必须完整、就近、屏蔽,噪声敏感区必须隔离、单点、干净。

最后说一句废话,EMI优化从来不是加个滤波器就完事,而是从芯片选型→频率规划→抖频开启→环路面积控制→布局细节每个环节的设计。