最近在尝试做一个可以多个并联的迷你电子负载,小体积方便放在桌面,上位机控制及显示电压、电流等状态

参数如下:

-

单个设备持续功率30W,测电源芯片动态响应时最大功率100W(也就是测试时给30%占空比)

-

至少三档可调电流上升沿时间:10us,100us,10ms

-

电流范围1mA~3A,高精度模式1mA~100mA,普通模式10mA~3A

-

最多三个设备并联,并联后所有设备的电流上升时间还是保持一致,仍然是10us,100us,10ms

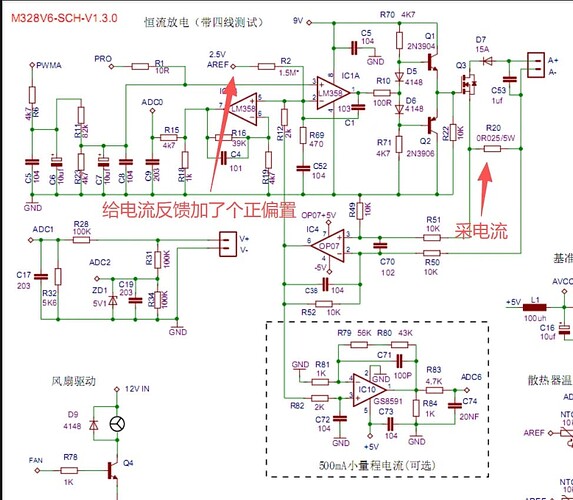

第一、二个功能没什么问题,已经实现,但是第三和第四个参数调试时发现运放输入失调电压的巨大影响,导致电流精度不足1mA,且三个设备上升沿时间同步有问题。 由于想要做到1mA精度的电流设定,所以想着用一个5uV失调电压的运放足够了,原本以为硬件上已经没有问题了,结果做主从设备同步时是还是发现了两个硬件上的问题,简单介绍一下万一能为读者避坑呢 ![]() 。

。

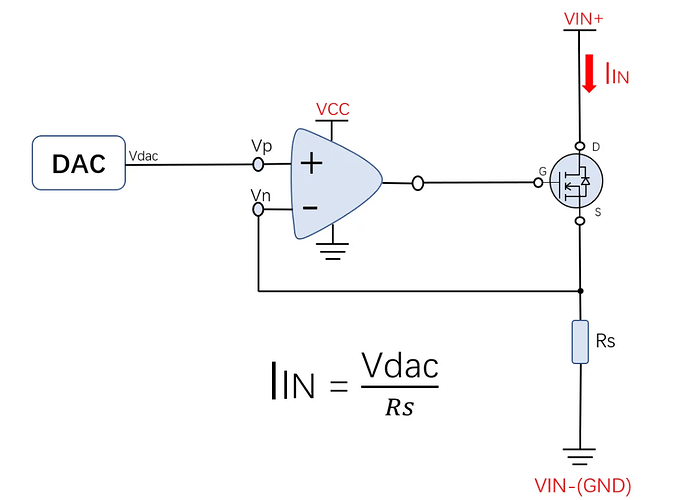

基本框架如下,DAC+运放+MOS构成,当运放与MOS形成负反馈后,由于虚短,运放Vn=Vp=Vdac,即采样电阻上端电压等于Vdac,因此电子负载电流IIN=IRs=Vdac/Rs

基本原理就是这么简单,如果电子负载想要输入电流为0,理论上DAC输出0V电压即可。但是由于运放存在输入失调电压,即**运放形成负反馈平衡时,两个输入端电压并非完全相等,存在失调电压Voffset(Vos),定义VOUT=A(Vp-Vn+Vos),也就是说运放要输出0V,需要满足公式所给的条件。

基于此条件有了两个问题:

第一个问题——无法完美关断(即电子负载吸收0A电流)

当需要设置电子负载输入0A电流时:

-

Vos>0,电流为0时运放负输入端Vn=0,VOUT=A(Vp-Vn+Vos)>0,那么DAC要输出小于-Vos的电压才能保证运放输出电压向负电源轨(0V)偏移而使IIN为0,但是由于DAC是正电压供电,不可能输出负压,这就导致VOUT=A(Vp-Vn+Vos)永远大于0,因此该条件下无法实现电子负载输入电流为0A。

-

Vos<0,电流为0时运放负输入端Vn=0,VOUT=A(Vp-Vn+Vos)=A(Vp+Vos)<0,那么DAC只要输出小于Vos绝对值的电压就能保证运放输出电压为0,因此这个条件可以实现电子负载输入0A电流

第二个问题——失调电压导致的状态不确定进而导致同步延迟:

-

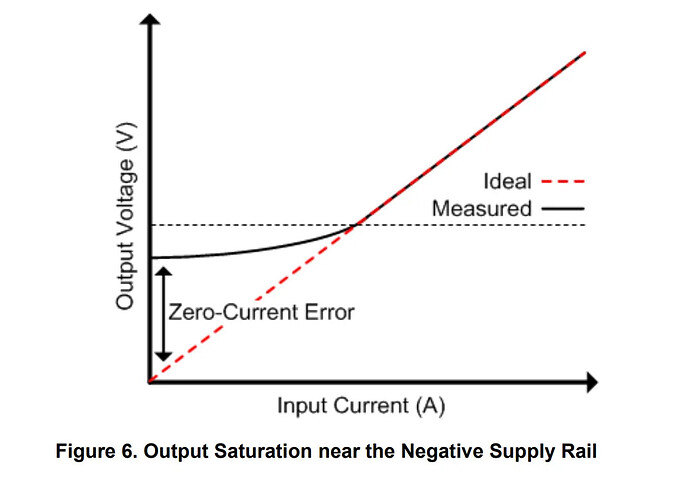

Vos>0,电流为0时运放负输入端Vn=0,即使Vp=0,VOUT=A(Vp-Vn+Vos)>0,运放输出向着正电源轨偏移,直到电子负载吸收的电流在采样电阻Rs上产生的电压即Vn=Vos时,Vout才平稳,此时运放输出电压大约就等于MOS管的开启电压大约3V。

-

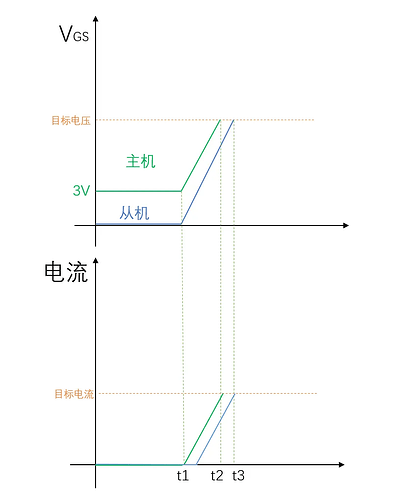

Vos<0,电流为0时运放负输入端Vn=0,VOUT=A(Vp-Vn+Vos)>0,运放输出向着负电源轨偏移,直到接近运放负电源轨(0V),因此平衡时运放输出电压接近0V。 当需要主、从机同步吸收电流保证总的电流上升沿斜率一致时,理论上只需要通过IO触发同时让DAC输出一个相同的电压即可,但是由于前面说的Vos正负差异,导致两种情况下运放输出电压起点不同,例如一个0V开始,一个3V开始,且运放带宽和slew rate是有限的,这就产生了延迟。 如下图,t1时刻开始给定DAC电压,t2和t3代表实际上两个电流的延迟,实测可能超过5~10us,这个大小已经等于我的最快档位的10us上升时间了,会导致总的电流上升沿变形、延迟,不可接受。

这个问题总结来说:主从机同步的瓶颈不在于触发信号的纳秒级偏差,而在于触发前各环路静态工作点(因Vos极性不同)的物理差异,这个差异被运放的有限压摆率放大为了微秒级的电流上升延迟。

解决问题思路

那么如何解决这两个问题呢?

第一个问题原本想过,当时想着可以接受微小的例如100uA级别的静态电流,因此就选了个5uV失调电压的运放就完事了,但是现在想想不如直接解决它。第二个问题是必须解决的。

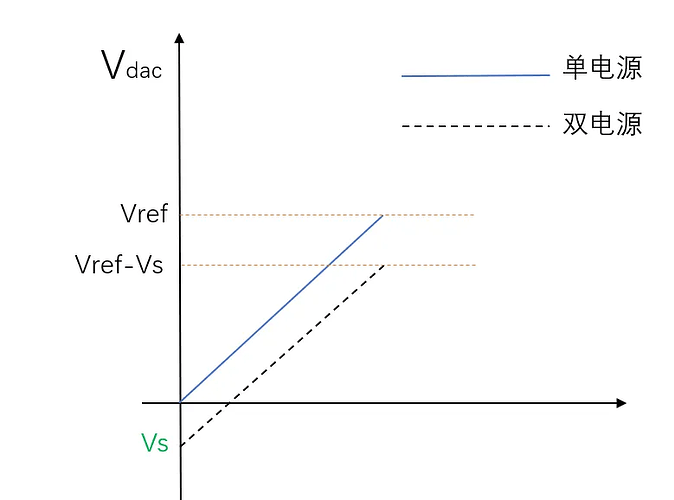

如何解决呢,首先再想要选择更小的失调电压的运放也没有意义,它总会存在的,只要存在就可能导致这两个问题。因此想要解决需要从DAC输出的电压不能低于0V下手,如果能达到-Vos的输出,就能保证无论Vos为正还是为负,VOUT=A(Vp-Vn+Vos)都能小于0,这样的话就不存在静态电流,也能保证每个设备的运放输出电压起点都是0V,设备间不会由于起点差异导致电流上升沿时间差异。