也就是说,为了兼容不同的电平:

MDC97476 的 IO 电平追踪 VDD 电源电压,即:

若 VDD = 5V → 输出 IO 电平为 5V 兼容;

若 VDD = 3.3V → IO 电平为 3.3V;

多数 MCU/FPGA IO 电平 仅支持最高 3.3V ,若 VDD 配成 5V,直连会烧坏外部芯片 IO 口 。

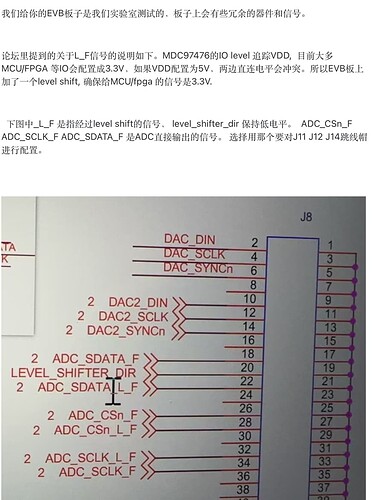

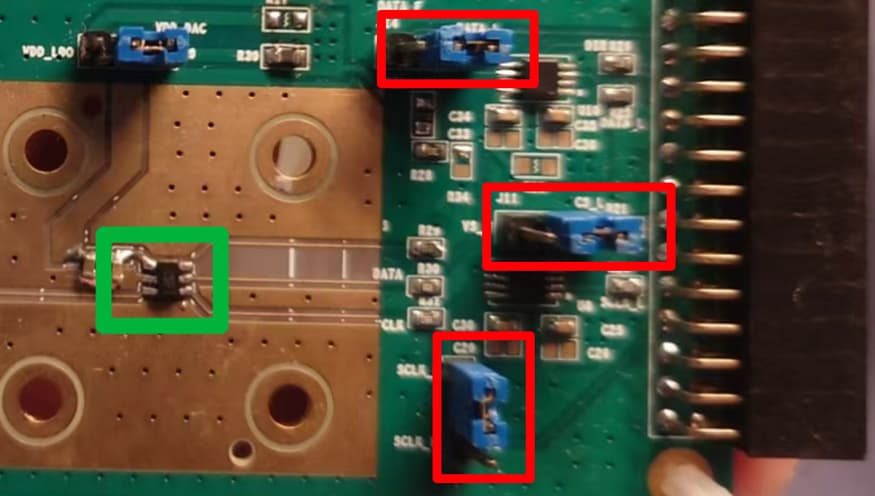

EVB 板上添加了 电平转换器(Level Shifter ) 来适配这个问题:

| 信号名(带 _F) | 含义 |

|---|---|

| ADC_CSn_F | 原始 ADC 输出信号 (高电平,跟随 VDD) |

| ADC_CSn_L_F | 经电平转换后的信号 (恒定 3.3V 兼容) |

“_L_F” 后缀中的 “L” 表示 Level shifted 的版本。

那上面的 DAC 是什么意思?