各位“攻城狮”朋友们,上一篇文章中我们分析了汽车 DCDC 的 EMI 两大噪声源,接下来让我们来讨论大家非常关心的汽车 DCDC EMI 优化。

点击上图或下方链接可跳转至视频

视频文字部分:

一个DCDC系统能够通过严苛的CISPR 25 ,离不开两点:

- 需要一个EMI性能优秀的电源芯片

- 丰富的系统EMI设计经验

图1

本期我们将从芯片设计角度出发,讨论下DCDC具备哪些特点,EMI性能才比较优秀。

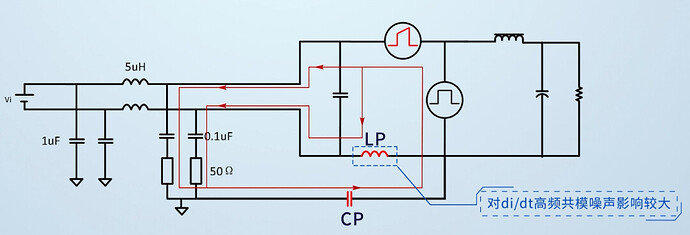

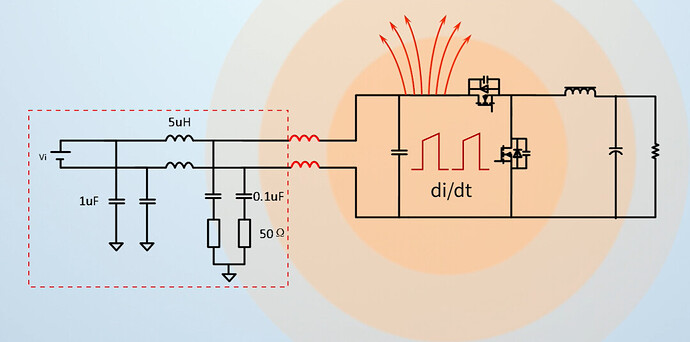

大家知道DCDC的两大噪声源是di/dt噪声和dv/dt噪声,今天我们还是从这两大噪声源出发,来讨论下芯片设计是怎样优化这两大噪声源的。

di/dt 共模噪声的优化

前面的电源小课堂我们分析了,寄生电感Lp对di/dt高频共模噪声影响较大,Lp 越大,di/dt的高频共模噪声就越大,反之越小。

图2

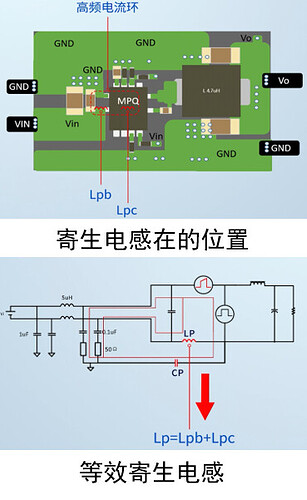

那么Lp在电路中是怎么产生的呢?

大家知道,任何走线都会产生寄生电感,这个寄生电感包含两部分PCB走线Lpb 以及芯片封装Lpc,如下图:

图3

所以减小Lp ,其实就变成:怎样减小高频电流环的面积,方法如下:

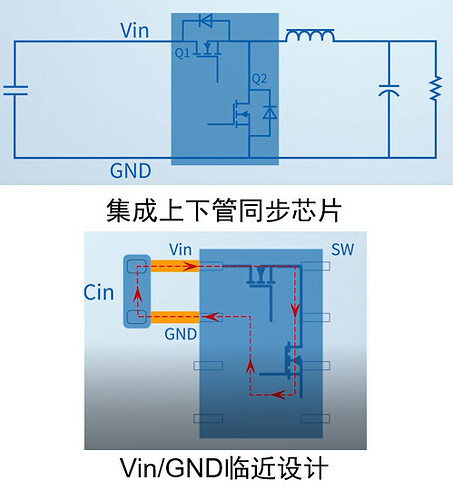

1. 芯片同步设计,且Vin和GND 管脚要靠近

如图所示,将上下管集成到芯片里边去,同时Vin和GND pin 脚足够近:

图4

这样CIN电容可以非常靠近芯片的,高频电流环足够小,PCB走线带来的寄生电感Lpb也可以控制的较小。

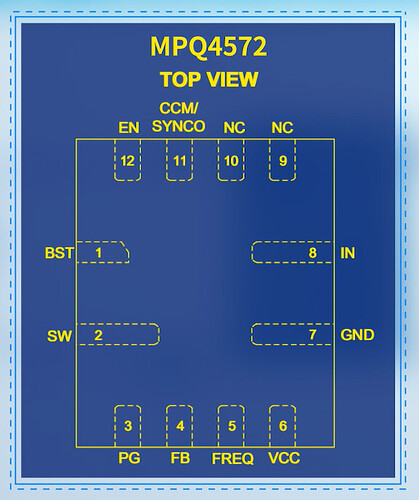

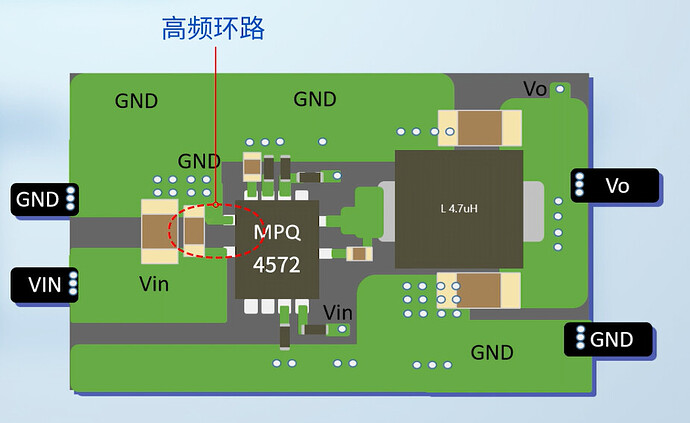

例如,我们明星产品MPQ4572就是这样的设计:

图5

看下MPQ4572的Layout,可以很方便地将高频环路,控制到红圈以内,寄生电感可以做到最小。

图6

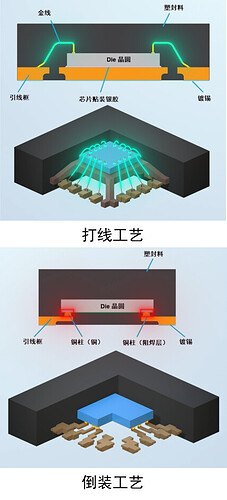

2. 第二芯片采用flip clip封装,减小内部寄生电感Lpc

常用的封装有两种方式:

- 一种是打线工艺,用金属线将晶圆和封装焊盘连接的方式,由于很长的Bonding线将产生很大的寄生电感

- 另一种是倒装工艺,采用铜柱子连接晶圆和封装引脚,铜柱子短且粗,寄生电感将大大降低

图7

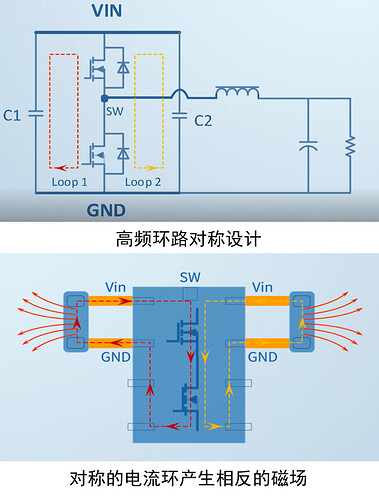

3. 芯片VIN/GND高频电流环对称设计

di/dt除了产生差模共模噪声外,还会产生近场磁场耦合问题,由于输入测试的线束上有寄生电感,di/dt产生的磁场,很容易耦合到输入线束上,从而产生EMI问题。

图8

为了优化近场磁场的耦合,可以将输入高频电流环对称设计。

图9

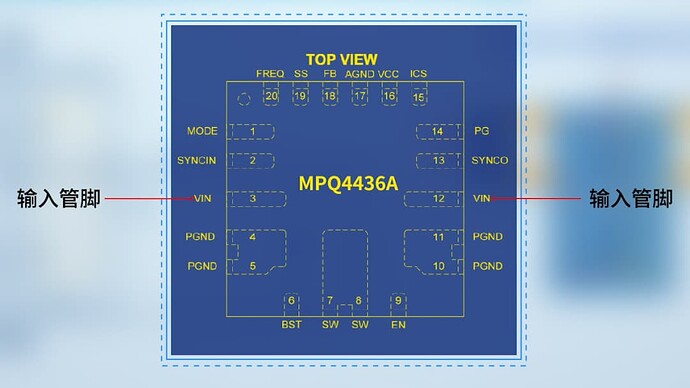

对称的高频电流环,电流向正好相反,产生的磁场方向也相反,磁场可以相互抵消,可以减小近场磁场的EMI耦合。我们的明星产品MPQ4436A的输入管脚就是对称设计的。

图10

dv/dt 共模噪声的优化

上一期电源小课堂我们分析了dv/dt产生的是一个共模噪声那么针对dv/dt共模噪声的抑制,比较好的办法是减小dv/dt了。

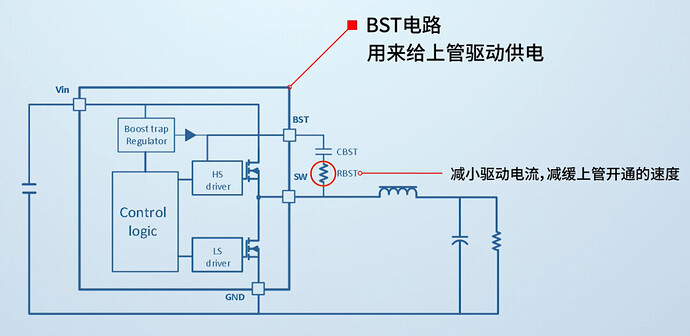

一般DCDC都有BST控制电路,可以利用BST电路来减小上管开通时间。BST 电路是用来给上管驱动供电的(上管Q1 Gate供电来自BST 电容),在BST 电容上串一个限流电阻,可以减小驱动电流,从而减缓上管开通速度。

图11

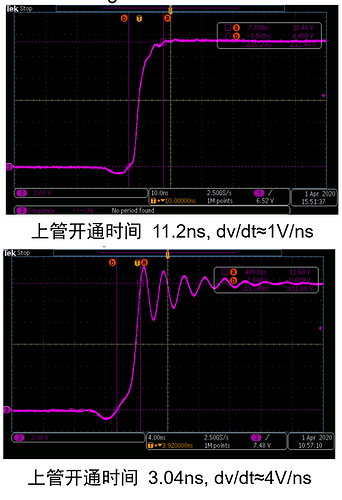

我们来看一个对比,不同上管开通时间,SW波形的变化,更缓的开关速度,不仅dt变大了,而且也减小了dv,从而dv/dt噪声将成倍数降低。

图12

抖频技术来优化EMI

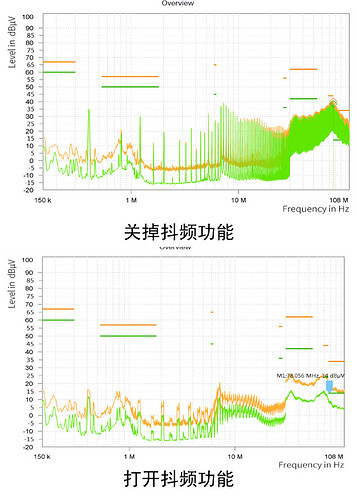

抖频技术是将固定的开关频率按照一定的规律将频率分散在一定范围变化,这样可以减小基频以及倍频的EMI噪声。

我们来看看开抖频和关抖频,EMI测试的比较,抖频对传导全频段都有较大帮助。

图13

综合以上讨论,如果一个电源芯片具备以下6点功能,这颗芯片的EMI性能将非常出色。当然,有些芯片不能同时具备以下6点,那么1/2/5是基础的要求:

同步集成上下管

VIN/GND pin 脚临近设计

采用倒装的封装工艺

VIN/GND 高频电流环对称设计

BST电路设计

抖频功能

今天我们介绍了电源芯片本身跟EMI性能相关的特点,希望对大家选择车规级DCDC芯片时,有一定的帮助,我们下期将带来汽车DCDC 系统EMI优化设计, 请大家持续关注MPS电源小课堂。

> 如有相关需求可点击 MPS NOW 在线技术支持, 工程师将为您直接提供项目技术支持服务

> 查看更多技术资源可访问: Resource Center (monolithicpower.cn)