要提高电源效率,降低发热,我们要分析一下电源的损耗来源。电源的损耗都是转化成了热能,降低损耗就是降低发热。本文以buck为例进行分析。

在之前的文章中我们介绍过buck电路的工作原理:

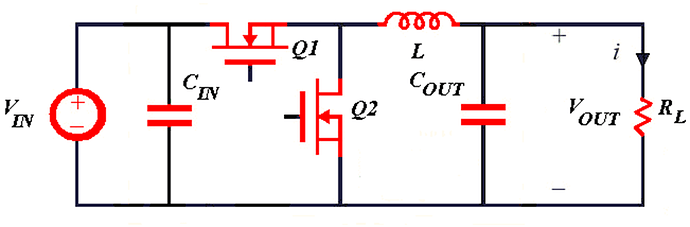

buck拓扑如下图:

先上结论:

I. 对于集成MOS的电源芯片来说,MOS的导通阻抗已固定。一般来说,选择导通阻抗更小的MOS,效率会更高。

II. 对于外置MOS的电源芯片来说,选择导通阻抗更小、Qg更小的MOS可有效降低开关损耗及导通损耗。但是导通阻抗更小的MOS往往意味着Qg更大,因此需要评估在某一条件下开关损耗与导通损耗的占比,如果开关损耗占更大比重,那么选择Qg更小而导通损耗更大的MOS,也可能可以降低整体损耗,需要视整体情况而定。这是很多工程师常犯的错误,在控制器方案中,并不一定是选择导通阻抗更小的MOS就能获得更高的效率。

III. 适当减小开关频率。减小开关频率可降低开关损耗。不过需要注意的是,减小开关频率会使得电感电流纹波值变大,如果电感电流纹波值过大,也会引起更大的损耗。因此建议在减小开关频率的同时,增大电感的感量以确保电感电流纹波值不会过大。

IV. 选用DCR更小的电感,减小电感上的损耗。

V. 如果对于轻载效率有较高要求,需要选择轻载效率较高的芯片。轻载高效的芯片一般在设计时就尽可能降低了逻辑控制电路损耗,也通过降低开关频率降低了开关损耗、驱动损耗。

下面我们来具体分析。一般来说,buck电路的损耗主要有开关损耗、导通损耗、电感损耗、驱动损耗、逻辑控制电路损耗等。大多数情况下,以开关损耗、导通损耗、电感损耗为主,其余损耗基本可忽略不计。

1. 开关损耗

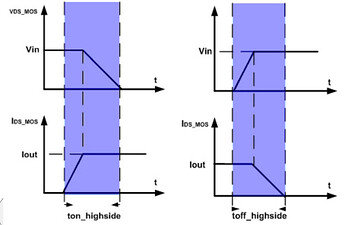

开关损耗包括开通损耗和关断损耗两种。开通损耗是指功率管从截止到导通时所产生的功率损耗;关断损耗是指功率管从导通到截止时所产生的功率损耗。

所谓开通损耗,是指非理想的开关管在开通时,开关管的电压不是立即下降到零,而是有一个下降时间,同时它的电流也不是立即上升到负载电流,也有一个上升时间。在这段时间内,开关管的电流和电压有一个交叠区,会产生损耗,这个损耗即为开通损耗。关断损耗同理。

在buck电路中,下管Q2由于体二极管的存在,几乎都是0电压开通和0电压关断,因此下管Q2的开关损耗几乎可以忽略不计,开关损耗主要存在于上管Q1。Q1的开关损耗大小可通过下面的公式计算得到

ton_highside是上管Q1从关断到导通所需时间,或者说是开通过程中电压与电流的交叠区域的时间。toff_highside同理。ton_highside和toff_highside与MOS的Qg和芯片的驱动能力有关,芯片的驱动能力越强,MOS的Qg越小,驱动所需时间越短,ton_highside和toff_highside越小,开关损耗越小。

从公式可以看出,在输入电压、输出电流固定的情况下。降低开关频率可以降低开关损耗。

2.导通损耗

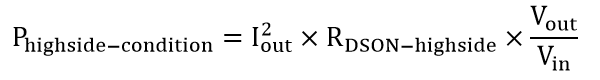

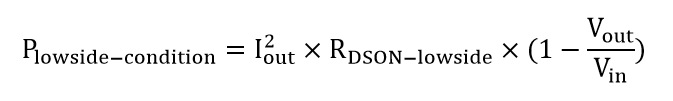

MOSFET在导通时是存在导通阻抗的,其特性近似为一个电阻,一般用RDS_ON表示。在导通阻抗上产生的损耗即为导通损耗

上管的导通损耗如下,Vout/Vin即为上管导通时间占整个周期的比值

下管的导通损耗如下,1-Vout/Vin即为下管导通时间占整个周期的比值

3.电感损耗

电感上的损耗分为磁芯损耗和线圈损耗两部分,大多数情况下磁芯损耗可忽略不计,线圈损耗主要是由电感线圈等效电阻DCR产生,其损耗可由下面的公式计算得到:

4.驱动损耗、逻辑控制电路损耗

一般来说在重载时,这些损耗占比都很小,几乎可以忽略不计。但是在轻载时,这部分损耗会占有一定的比重。因此如果对于轻载效率有较高要求,需要选择轻载效率较高的芯片。轻载高效的芯片一般都是DCM模式,包含AAM、PSM、USM等。